- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计:内同步时钟系统

共同时钟系统还有一个特例就是内同步时钟系统,很多经验不足的工程师,会把内同步时钟系统误判成源同步时序,按照源同步时序的方式来进行等长控制,导致时序设计错误。

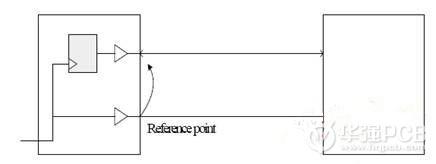

首先,我们来回顾一下怎么判断一个系统是共同时钟,之前的博文提到,找时钟树,确定时钟信号的关系,是判断各种时序系统的关键。共同时钟系统,一般有一个外部的晶振或者晶体,然后通过时钟分配器分别连到系统的驱动端和接收端(也可以是FPGA直接输出不同的时钟到驱动端和接收端),由外部时钟线来控制系统的时序工作方式,叫共同时钟系统。

内同步时钟的时钟信号是从驱动端直接发到接收端的。之前的博文提到,共同时钟系统时序裕量较小,频率无法继续提升的一个关键因素之一就是Tco,受限于工艺等因素,这个Tco很难做到太小,比如SDRAM的Tco max一般有5.4ns。内同步时钟系统把外部时钟驱动器换成了内部的Buffer,这样时钟信号上的Buffer可以和数据信号的Buffer匹配起来可相互抵消,这样器件的Tco的最大最小值之间的范围可以减小,增加时序裕量,使得时序容易满足。

图1

内同步时钟系统容易和源同步搞混,其实把握一个原则就很容易区分,源同步时序一般都存在系统时钟和数据组的Strobe信号,比如DQ和DQS和CLK之间的关系。而内同步时钟就只有一个驱动端接收端共用的时钟信号(在Mobile SDRAM中,信号名是SDCK)

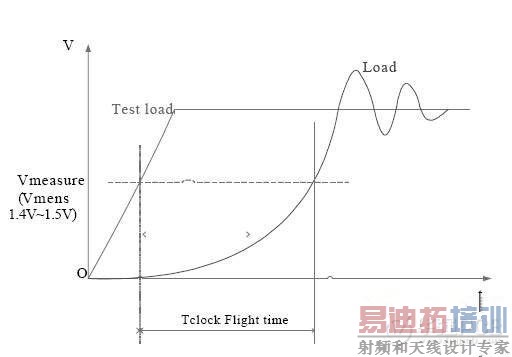

所以内同步时序在计算上,和共同时钟类似,只是在不等式上多了一个变量,就是TCLK_FT : Clock的Flight time,图2为TCLK_FT的测量方法。

图2

内同步时钟的时序计算公式为:(当时钟与数据的传播方向相同时为正方向)

Tco(max)+Tflight(max)+Tsetup-Tclk_ft+Tjitter+Tmargin<Tcycle

Tco(min)+Tflight(min)-Tclk_ft-Tmargin>Thold

这样可通过调节Tclk_ft使时钟处于最佳位置。同样在外同步方式中也可以利用这一方法来调节时序。具体的调节方法在之前的案例中已经进行了介绍,大家可以参考。

总结:

从外部来看,内同步和源同步方式一致,但是两者的内部结构不同。源同步方式是在内同步的结构上在时钟信号的Buffer之前增加了一个寄存器,芯片内部对时钟处理和数据的处理一样。这样时钟可以跟着数据的速度变化,始终在数据中间。

而内同步时钟的本质还是共同时钟系统,时序计算和外部时钟的共同时钟系统一样,只是在计算结果两端要加上或者减去Tclk_ft。时序约束关系也是总长度最大最小值的方式,不是等长的方式。

内同步时钟增加了时序裕量调节的手段,并且因为抵消了Tco的影响,时序更加容易满足。但是时序计算方法更加复杂,需要设计工程师进行把握。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...