- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高频电路板的线路设计工艺

对于高频线路,走线的合理性直接影响到电路的性能。在高频电路板线路的设计中(尤其对10MHz以上的频率),为了能够得到应有的高频电路特性,必须注意以下几点:

1、地的高频阻抗值。

2、走线所产生的电感成分。

3、电路间的高频偶合。

一、应尽量将地的高频阻抗值降低

在低频电路中常采用一点接地,使各接地点成为同电位。在高频电路中也同样必须使电路的各接地点电位相同。

但是在高频电路中往往由于走线较长,要达到一点接地较为困难。因此,如何使地的阻抗值降低,使各接地点的电位尽量相同,是相当重要的。

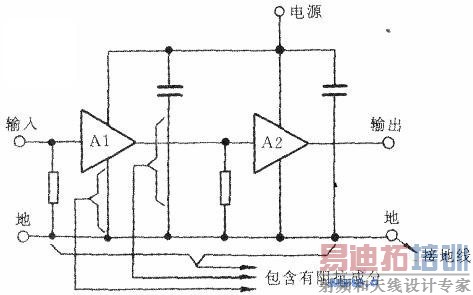

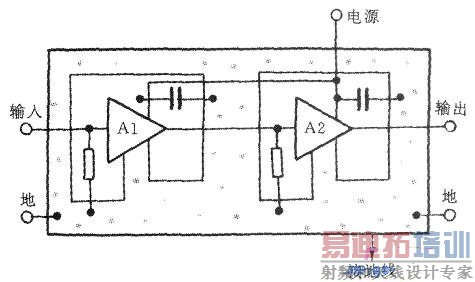

上图所示电路的接地对于低频电路不会有问题。但对于高频电路而言,由于接地线有电感成分,其阻抗XL=2πfL,频率愈高此一阻抗值也愈高,使得图l 各接地点无法成为同电位。在高频电路中常使用铜箔来做成大面积接地方式如下图所示,此种大面积接地对于低频电路而言,相当于在接地的各处形成回路,较容易产生电磁感应。但对于高频电路而言,则由于接地面积愈广电感量成分愈小,电路的各接地点较易成为高频率之同电位。

二、应将走线所产生的电感成分极力降低

在高频电路中,连接各元件的走线具有电感量成分。配线愈长电感量成分愈高,会使频率特性恶化(由感成分和杂散电容形成低通滤波器),也可能发生振荡(由于电感成分使相位偏离)。

因此,原则上走线要粗短,元件的排布要按此原则进行。且插脚式晶体管、电阻、电容等元件的端子具有电感成分,当频率很高时不可以忽略不计。因此,元件的端子也应该尽量缩短。最好在高频电路中采用贴片元件以减少元件端子的电感量。

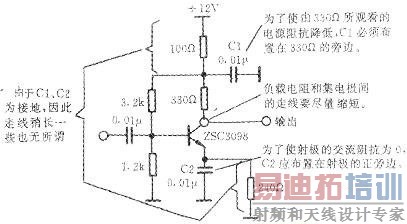

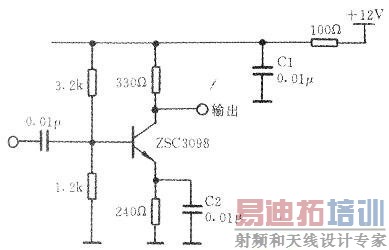

例如上图所示电路,在高频电路的元件布置时,应采用下图的布置方法。

将Cl(电源的去耦合电容)尽量布置在靠近负载电阻(330Ω)的旁边。C2为射极旁路电容,也应尽量装配在靠近晶体管的射极旁边。

三、防止电路间的高频耦合

信号频率愈高、滤长愈短,便愈容易成为电磁波发射到空中。因此,对于几十MHz上的信号,大多应采用铜片或镀锡铁片将电路全体隔离,以防止电路内部和外部高频的耦合。在同一电路内,为了防止电路内部的耦合,也可采用隔离方式处理,并将隔离罩接地,亦可降低接地地阻抗。另外,在电源供给线上串连电感或磁环,并可加入贯穿电容,以防止高频经电源线耦合。

以上几点在走线中必须注意,才能得到应有的高频特性。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:线路板厂话你知----什么是库存周转率

下一篇:电路板厂覆铜板介绍