- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCB板阻抗控制

近年来,随着IC集成度的提高和应用,其信号传输频率和速度越来越高,因而在印制板导线中,信号传输(发射)高到某一定值后,便会受到印制板导线本身的影响,从而导致传输信号的严重失真或完全丧失。这表明,PCB导线所“流通”的“东西”并不是电流,而是方波讯号或脉冲在能量上的传输。上述此种“讯号”传输时所受到的阻力,也称为“阻抗”,代表符号为Z0。所以,PCB导线上单解决“通”、“断”和“短路”的问题还不够,还要控制导线的阻抗问题。

((一)) 何谓阻抗

阻抗是用来评估电子元件特性的一个参数。阻抗的定义是元件在既定频率下对交流电的总对抗作用。

((二)) 为何要阻抗控制

因为PCB传输线中的特性阻抗值必须匹配Driver与Reciver的电子阻抗,否则会造成讯号能量的反射、衰减,以及讯号到达时间之延误,严重时无法判独及开机。电路板线路中的讯号传播时,影响其“特性阻抗”的因素有线路的截面积,线路与接地层之间绝缘材质的厚度,以及其介质常数等叁项。影响阻抗最多部分为:1、线宽,2、pp 厚度,3、介电值(FR-4 =4.3)其次是防焊厚度,侧蚀,铜厚.等等这些会改变磁力线分布, 进而改变组抗之变数,先了解组抗公差值要求,再反推製程最大公差值,以软体计算是否可达成。PCB 製程管制重点为用对材料/线径公差10%以内/压后层间厚度準确10%以内,即可达到设计要求。

((三)) 何谓Er值

通常介质常数或称相对电容率既是每单位体积的绝缘物质在每一单位之电位梯度下所能储存的静电能量。介质常数高则信号传输不少被储存在板材中而造成信号不佳及传播速率减慢。一般对于信号品质要求高者会限用PTF((铁弗龙))就是因为其Er=2..5。

(四) 一般阻抗分3类:

1. 特性阻抗(impedance)。

如客户针对4层板,外层线宽进行阻抗之控制,其计算外层线宽阻抗软件模式如下。

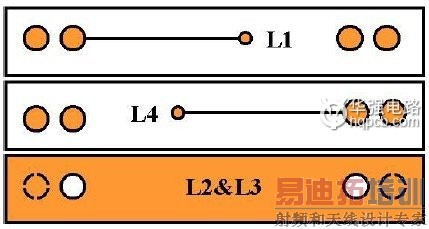

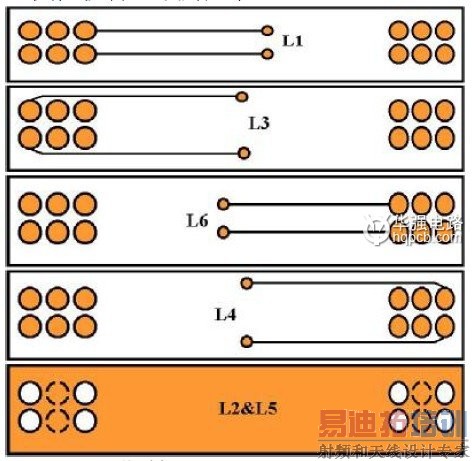

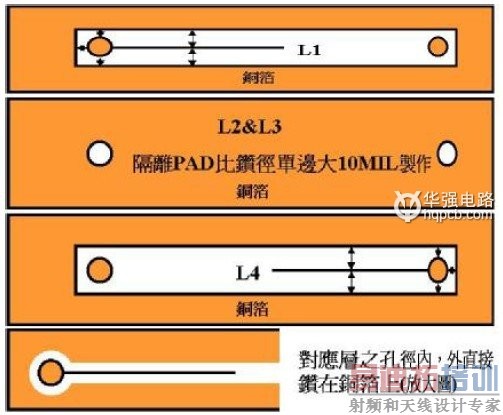

其阻抗条之设计如下:

如客户针对6层板,其1,3,4,6层为走线层,皆须进行阻抗线宽之控制,注意内层L3&L4之阻抗线宽需措开不可重叠,避免影响阻抗值之测试,其计算内层线宽阻抗软件模式如下。

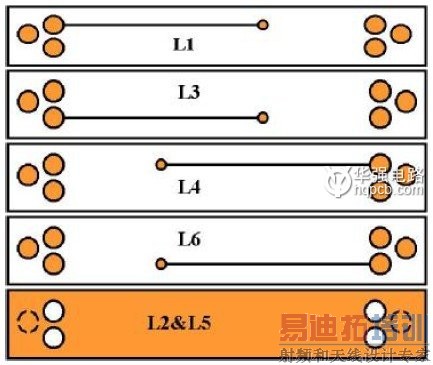

其阻抗条之设计如下:

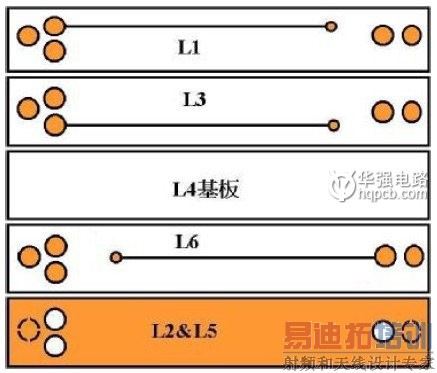

如客户针对6层板,其1,3,6层为走线层,皆须进行阻抗线宽之控制,其阻抗条之设计如下:

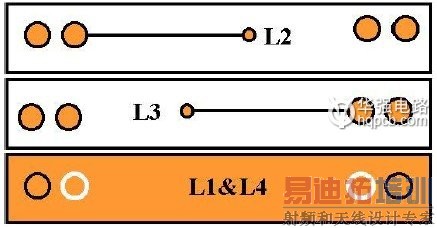

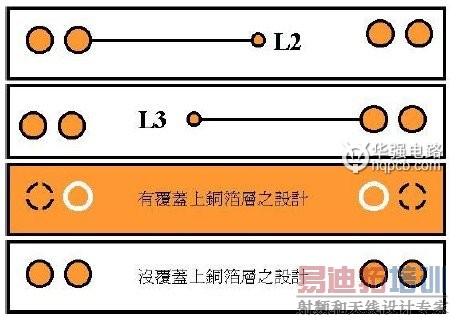

如客户针对4层板,内层(2,3层)线宽进行阻抗之控制,注意阻抗线宽上下对应层皆铺设铜箔,其L2&L3 之阻抗线宽设计需措开不可重叠,避免影响阻抗值之测试,其阻抗条之设计如下:

客户製作内层阻抗,需注意其要求之组抗线宽,上下对应层是否有覆盖铜箔或没覆盖铜箔,上下皆有覆盖上铜箔,其计算软件同上,如果有一层为没覆盖上铜箔,另一层有覆盖上铜箔,其阻抗计算软件模式如下。

其阻抗条设计如下:

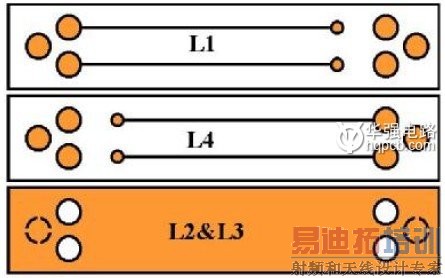

如客户针对4层板,外层&内层线宽进行阻抗之控制,注意内层之阻抗线宽需措开不可重叠设计,避免影响阻抗值之测试,其阻抗条之设计如下:

2.差动阻抗(differential impedance)。

客户针对4 层板,外层之线宽/间距/线宽进行阻抗之控制,其计算阻抗线宽/间距/线宽之阻抗软件模式如下。

其阻抗条之设计如下:

如客户针对6层板,其1,3,4,6层为走线层,皆须进行阻抗线宽之控制,其计算内层线宽阻抗软件模式如下。

其阻抗条之设计如下:

3.RANBUS阻抗。

客户针对4 层外层某种线宽/间距进行阻抗线宽控制,其计算外层RANBUS阻抗软件模式如下。

其阻抗条之设计如下:

客户针对6 层(1,3,4,6)某种线宽/间距进行阻抗线宽控制,需注意内层阻抗线宽需措开,不可重叠,避免影响阻抗值之测试,其计算内层RANBUS阻抗计算软件模式如下。

其阻抗条之设计如下:

(五) coupon设计注意事项:

1. 一般阻抗之设计有设计层(线路层),及参考接地层(对应层),如客户无规格限定,4层板之规格为L1(设计层)-L2[L2接地层(对应层)],L3[L3接地层(对应层)-L4(设计层)。

2. 内层有阻抗控制需注意,如连续2层皆有线宽控制,无其他层别[接地层铜箔(对应层)]阻隔,其线宽之设计需措开,不可重叠,避免影响阻抗值之测试。

3. 一般外层阻抗线宽需有铜条保护,其铜条宽度”越宽越好”,间距需min 10 mil以上。

4. 内层走线层,有阻抗控制需注意其上下接地层(对应层),是否有铜箔覆盖,其阻抗计算软体及阻抗条之设计不同。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:湿膜的优点介绍

下一篇:PCB板钻孔工艺缺陷及排除方法