- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB板设计中的串扰问题和抑制方法 (下)

UltraCAD Design开发了一些免费的计算器软件供设计人员使用,其中一个就是串扰计算器软件。它包括了以上几种串扰结构的计算,可用于估计邻近走线间的串扰系数,且简单方便。由于影响串扰的因素很多,所以软件不可能给出十分精确的结果,而是在最坏情况下的大概值,因此设计中还应参考以前的电路板设计对结果进行校准。

;

串扰的分析

使用EDA工具对PCB板的串扰进行仿真,可以在PCB实现中迅速地发现、定位和解决串扰问题。本文以Mentor公司的仿真软件HyperLynx为例对串扰进行分析。

高速设计中的仿真包括布线前的原理图仿真和布线后的PCB仿真,对应地,HyperLynx中有LineSim和BoardSim。LineSim主要针对布局布线前仿真,它可将仿真得到的约束条件作为实际的布线约束,较早地预测和消除串扰问题,从而有效地约束布局和变化叠层,并在电路板布局之前优化时钟、关键信号拓扑和终端负载。BoardSim则是针对布局布线后仿真,它可以精确地预测未知的PCB导线之间的耦合影响,将仿真结果显示在一个示波器中,并显示所有串扰波形的详细细节。其目的是为了预测和发现实际成品的串扰问题,从而节约设计者的时间,避免反复设计制造原理样机。

对布局布线前仿真而言,LineSim需要首先建立一个基本的耦合模型,对不同电路环境设置不同的约束条件,主要包括导线间距、最大平行长度、最大驱动IC的转换速度、介质的厚度、叠层结构等。这些约束可以让设计者在设计早期了解可能产生问题的地方,从而进行有效地计划,减少布局布线前可能出现的串扰,并找到最精确的约束条件,作为下一步布局布线的约束。在驱动芯片的选择方面可以引入IBIS(Input/Output Buffer Information Specification)模型,它一般由芯片厂家提供。

在运用BoardSim对布线进行串扰分析时,可以有以下3种方式:交互式的串扰仿真、快速批处理方式和详细批处理方式。其中,交互式串扰仿真可以直观地通过数字示波器观察干扰情况。这里提出了几何门限和电气门限的概念。几何门限会规定一定的区域,凡是进入此区域、具有一定长度的网络都被认为是攻击网络;电气门限会规定一个干扰量,凡是对本网络造成超过这一量值的干扰网络都被认为是攻击网络。采用几何门限需要设计者对串扰有一定的了解,知道在多远的距离、在哪一层会产生多大的串扰。因此通常推荐使用电气门限,它能更加准确,分析速度更快。

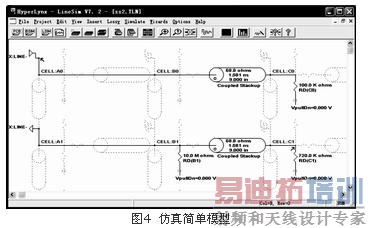

这里以TD-SCDMA终端基带电路中的ADC和DAC芯片MAX19700为例,说明对其时钟线的串扰抑制。首先要用一个简单模型来代表时钟电路,由LineSim建立模型如图4。

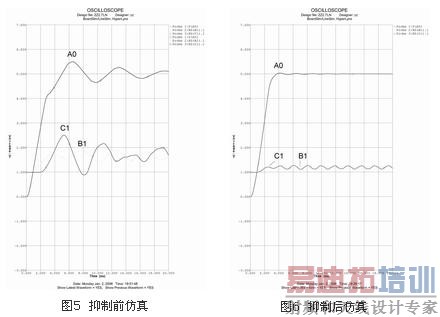

该基本模型有两个网络:驱动器A0(驱动线路为时钟信号线,其工作频率为5.12MSPS),通过传输线连接到1MW的电阻C0上;接收模式的驱动器A1,通过传输线连接在720KW的电阻C1上。每一条被耦合的传输线的特征阻抗都是68.8W,耦合长度是9in。HyperLynx计算出每条线上的延时大约是1.581ns。模型分为8层,设定两个信号线都为内层线(及微带线)且为同层。在PCB布局布线约束条件中,线宽为5mil,线间距为5mil,相对介电系数设置为4.3。图中分别在A0、B1、C1处加上了示波器探头,可利用示波器观看波形,B1的10MW电阻也是为了加探头而设置的。仿真结果如图5所示。

从图5中可以看出串扰的幅度比较大,因此需要采取办法抑制串扰。图6的仿真波形是修改了简单模型的约束条件而得到的,主要修改了信号的结构,将两个网络分别放到了不同的层里,耦合长度也减短为3in,由图6可知串扰得到了明显的抑制。将这一约束条件直接带入下一步的布局布线中,可以抑制串扰,且不需再单独对这一网络进行BoardSim仿真,节省了时间。

串扰的抑制

不管是设计前的串扰计算,还是布局布线前的仿真,或是布局布线后的仿真,都是为了使PCB板能快速达到最小的干扰。因此需要在设计过程中运用以前的经验来解决现在的问题,以下就是有效避免布局布线中串扰的经验总结:

1)容性耦合和感性耦合产生的串扰随受干扰线路负载阻抗的增大而增大,所以减小负载可以减小耦合干扰的影响;

;

2)尽量增大可能发生容性耦合导线之间的距离,更有效的做法是在导线间用地线隔离;

3)在相邻的信号线间插入一根地线也可以有效减小容性串扰,这根地线需要每1/4波长就接入地层。

4)感性耦合较难抑制,要尽量降低回路数量,减小回路面积,不要让信号回路共用同一段导线。

5)避免信号共用环路。

在高速PCB设计的过程中,不仅需要对理论概念的详细理解,同样需要不断的积累经验,不断完善理论。同时,对相关辅助软件的熟练运用也可以缩短设计周期,从而提高竞争力,对设计的成功完成起到重要的作用。

结语

高速PCB板级、系统级设计是一个复杂的过程,包括信号串扰在内的信号完整性问题越来越不容忽视,因此需要设计者在设计的时候对信号完整性问题有全面的规划与考虑,在设计周期的各个阶段采用不同的方法来确保设计快速、精确地完成,从而节约时间、避免重复。

**************************************************************

更多内容:高速PCB板设计中的串扰问题和抑制方法 (上)

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB布线中的抗干扰设计

下一篇:高速PCB板设计中的串扰问题和抑制方法

(上)