- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于DDR信号辐射问题

我看我师父的DDR1供电和参考电压引脚周围都放的是几个100n的贴片电容,稍远一点就是220微法的铝电解电容(看其他的参考设计也是这样)。请问高手是不是DDR附近一定只能放100n的电容(上面的设计是否有问题),还有就是是否有降低辐射的好办法。我是新手,问题有点低级,麻烦各位了

你把测试报告贴出来呀:超了多少个dB?(把频谱图贴出来吧)

还有就是把DDR这块PCB也贴出来!(几层板?把DDR这快内层分割也贴出来;还有把线款线距也说说.尽量说详细点吧)

你这样问那些大牛们怎么给你回答呀

回复

xyy_zhong

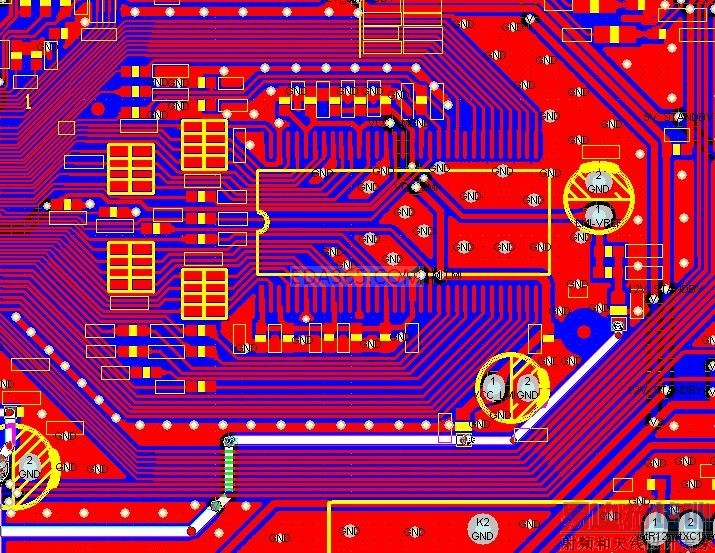

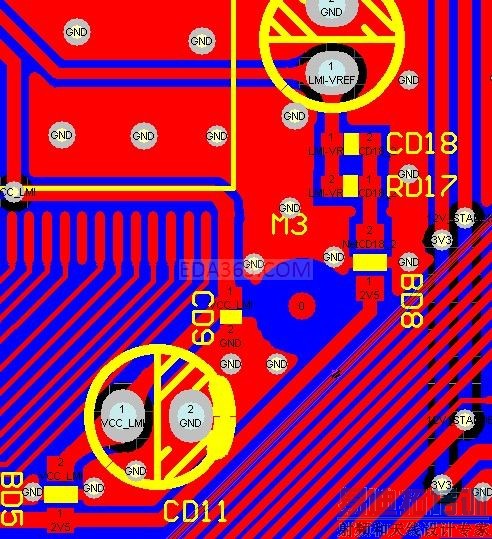

这是DDR的整体局,加亮的是2.5v供电,这个板子是两层板,其中靠近DDR的两个电解电容为10微法、100微法

其中BD5,BD8是121的磁珠,线宽为0.2mm,

线距在0.15mm左右,做测试时133MH超了4个dB,666MHz超了1个dB,其他频点都很好

楼主这板画的还挺漂亮的耶!

个人看法仅供参考:

1、你的时钟是单端的还是差分的呀,信号波形如何.你的2.5V电源需要加粗,DDR芯片引脚加强滤波.

2、你的DDR地层是不是走了线了,你可以用0欧姆把DDR下面断了的地连接起.

3、你们有没的频谱分析仪器,你可以用电场探头和线圈找找源头.是信号线还是时钟引起的,是DDR这块还是CPU引起的.

在这里的电容主要是做电源去耦的

从电源完整性的角度去看是要通过计算和仿真来得到结果,对于相对简单的应用(你们的板都布成2层了....)参考DDR设计建议里面的电容值进行原理图设计就可以了。电容要尽量靠近IC管脚摆放,小电容受到其去耦半径的制约要最近摆放,然后是大电容,电解电容一般具有较大的容量即ESR、ESL可以不用离很近。连接小电容到IC管脚的布线要尽量的短和粗~。简单的讲,小电容针对高频,大电容针对低频。

对于你的板子,我觉得可以

1 适当加宽电源走线的宽度(空间还是有的),如果对IC送电网络的布线很长的话建议每800~1000mil就对电源网络加小电容对地(4.7nf经验值),过长的电源走线是很好的辐射天线。

2 注意下时钟线的布线,把它和其他信号线的间隔加大些能减少串扰,时钟信号千万不能跨分割布线

3 图不完整,注意检查下数据线是也出现下方地平面不完整的情况

4 有一点我看不太明白,你们地址线上串的电容应该是靠近源端的,咋会和DDR离这么近,一般的33R(or22R)是针对 50ohm特征阻抗网络布线的匹配电阻,很显然你们这个双层板的阻抗要大的多,适当调整排阻位置并试试加大阻值,低成本板一般都不做阻抗控制的,有些端接就要靠试验了,这点对波形肯定有帮助,但对EMI影响估计不明显

5 你这4dB是CLASS A?估计有点难度 板子要好好优化 --高速线号换层 电源和地网络--

1. 100nF 是一般值,可以調變,但是要仿真輔助。

2. 如圖下方的幾個去耦電容接的像是浮地,有灌孔到下面的參考層嗎?若無,則要補灌孔。

3. 兩層板而言,依你的線寬,特性阻抗可能都有一百多歐姆,時鐘線的串聯端接電阻可以適度加大到100歐姆左右。

首先谢谢你的帮助。其实这个板子不是我的,是我师兄的。我是新来的员工,

所以做EMI这些跑腿的活都是由我来做。不过做EMI实验收获还是挺大的。

1,我看了数据线下面地平面确实有被割开。

2. 用软件计算了一下,信号线的特性阻抗差不多到140ohm了,应该会影响信号波形。你说端

接电阻要尽量靠近源端,我看了靠近源端那边确实放不下了。(不过你说的经验确实很宝贵)

3. 想问一下,好多地方说加宽电源走线的宽度,但我感觉走线只要能够达到电流容量了,为

什么还要加宽啊。

谢谢你的建议。这个板子DDR下面电容有过孔到地,只是只打了3个过孔,

可能少了点。用软件计算了一下,信号线的特性阻抗差不多到140ohm了,

我试试用100ohm的端接电阻试试。另外我试了一下减小时钟差分电阻好像

也有效果的。

"3. 想问一下,好多地方说加宽电源走线的宽度,但我感觉走线只要能够达到电流容量了,为什么还要加宽啊。"

较宽的电源走线具有较低的等效电感,这样对于数字IC有较低的高频阻抗,提高电源完整性。

IC在低频情况下电流阻抗很小,但在高频下受到趋肤效应,以及高频本身特性就会导致阻抗过高。

一旦IC内部电路有瞬态电流要求时,高阻抗不能很好满足其电源平稳特性,可能会带来功能甚至是性能的问题

所以对于高速电路的电源线路,都要加宽些。

学习了!

学习了~~

学习了~~

高手好多啊 学习了

下载来看看,谢谢楼主

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...