- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

SPI总线上串联电阻与串行端接

录入:edatop.com 点击:

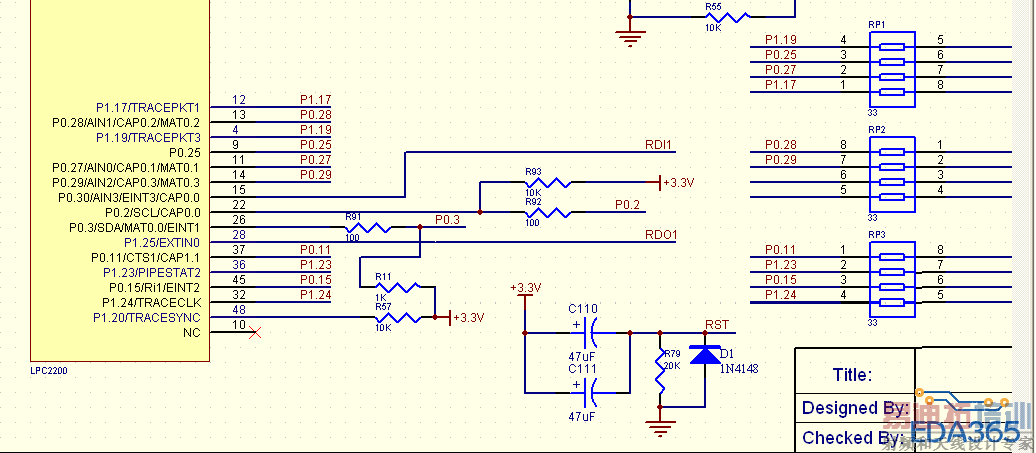

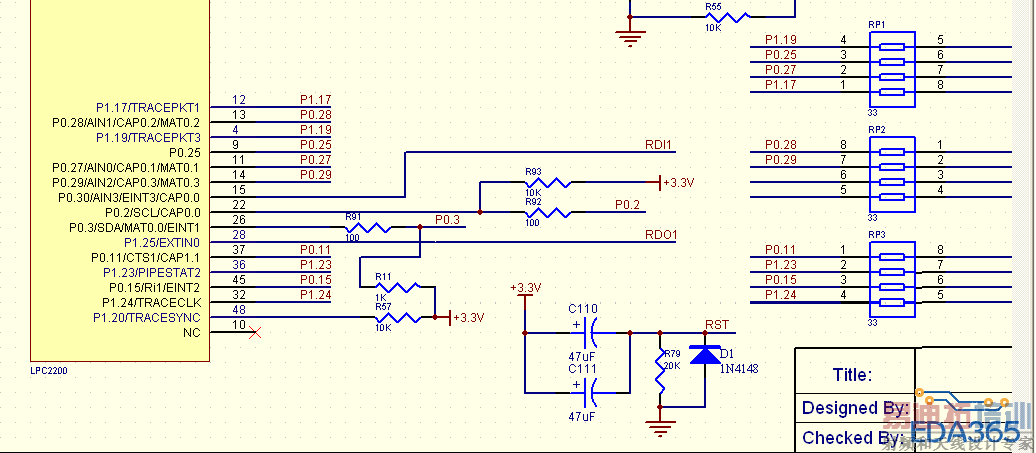

最近在进行ESD测试时发现,板子的SPI总线上耦合了静电,结果是把CPU打死了,去掉SPI总线上串联的电阻或增加电阻的阻值,无论怎么打ESD,都不会把CPU打死,SPI总线也应该没有问题,但现在的问题是,怎么滤掉SPI总线上耦合的静电呢?或者其他对SPI的防护措施?把电阻加到1K左右,真的不可以吗?

尝试过强制加上拉电阻,没有效果。ESD是水平耦合板和垂直耦合板测试!SPI总线是CPU引脚仿真的。

尝试过强制加上拉电阻,没有效果。ESD是水平耦合板和垂直耦合板测试!SPI总线是CPU引脚仿真的。

很古怪啊。串联电阻一般会提高抗ESD性能。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

上一篇:求助关于EMC test fail的原因分析

下一篇:最新电磁兼容培训资料