- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

去耦电容在PCB中的应用

摘 要:介绍在PCB板上添加去藕电容进行EMC和信号质量的优化设计方法。详细说明在添加去耦电容时,去耦电容取值大小的计算、电容类型的选择、去耦电容的摆放、不同线路的频率和上升速度大小、线路板各层之间以及时钟的自协调频率的配合、防止共振的产生等这些应用去耦电容时关注和考虑的内容。

关键词:去耦电容;PCB;高速设计

0 引言

去耦电容一般指去除在器件切换时从高频器件进入到配电网络中的射频能量的电容器件。随着PCB和MCM设计功能越来越多,复杂度越来越高,使用的频率也就越来越高。随着功能和速度的增加,瞬态电流也不断增加。由于设计越来越复杂,器件密度越来越大,时钟频率越来越高,上升速度越来越快,产生了越来越多的感应噪声,比如Delta2I、地弹或瞬态交换噪声,当这种噪声大到一定程度时,会影响集成电路的功能和性能,添加去耦电容可以减少这些噪声。由下面的图1我们可以看出某一块电源加上去耦电容和没加去耦电容的反跳波形区别。加了去耦电容的电源反跳波形看上去既光滑又平整,没加去耦电容的电源反跳波形则有很多毛刺。

图1 左侧为同一电路加有去耦电容时的电源反跳波形,右侧为无去耦电容的电源反跳波形

采用多层板的一个目的就是在信号层、电源层与地层之间产生较大的去耦电容,从而提供更好的去耦能力。在模拟布线设计中,去耦合电容通常用于旁路电源上的高频信号,这些高频信号的频率超出模拟器件抑制高频信号的能力。如果在模拟电路中不使用去耦电容的话,就可能在信号路径上引入噪声或者振动。

对于控制器和处理器这样的数字器件,同样需要去耦电容,这些电容的一个功能是用作“微型”电荷库。在数字电路中,如果执行开关动作时没有足够的电荷,会造成电源电压发生很大变化,会导致数字信号电平进入不确定状态,并很可能引起数字器件中的状态机错误运行。

1 去耦电容的计算

目前,电源和地平面的噪声通常通过对原型产品的测量或凭经验来控制,根据经验把去耦电容的容量设定为默认的值。实践中,去耦电容数量、容量值以及电容的放置位置都与频率有关,要确定其最佳值的确是件非常困难的事。为了正确预测电容的有效性,要精确考虑瞬态电流和电源实际的供电路径。做到了这一点,则电源/地平面上的噪声就可以看到了,也就可以通过在适当的地方放置适当容量的电容从而有效地控制其噪声。一般情况下,去耦电容是在某一特定的谐振频率、安装、引线长度、走线长度以及其它改变电容谐振频率的寄生参数下,以最佳滤波特性为基础获得的,同时也有一些比较粗略的算法。

算法一:由公式Q=Cdv

C=I/(dv/dt) (1)

算法二:在已知时钟信号的边沿速率时

(2)

(2)

算法三:在确定好决定要滤除的最高频率时,用下式来计算

(4)

(4)

算法四:如果粗略的估算的话,可按

C=1/f (5)

2 去耦电容的选用

对于时钟电路而言,去耦电容的选择,通常根据时钟或处理器的第一谐波来选择,有时,主要的射频电流是由三次或五次谐波产生的,此时就要考虑该相应的谐波。

同时还要考虑去耦电容的自谐振频率,高于自谐振频率,去耦电容开始呈现感性,去耦性减弱。当去耦电容引线太长时,电感增加,也会影响去耦性。当使用电源和接地层作为主要的去耦电容器时,要考虑这种自带的电容器的自谐振频率。如果电源层和接地层电容的自谐振频率与安装在板上的集总去耦电容的自谐振频率一样,将会产生强烈的共振,导致不能产生一个宽的去耦谱段效果。如果时钟同步频率恰恰也是这个自谐振频率值,那么这个板的去耦性能将非常差。该PCB将变成一个可能不符合要求电磁干扰要求的发射器。如果使用具有不同自谐振频率的附加去耦电容,可避免发生与PCB电源层和地层的共振。

对于高频滤波而言,陶瓷片电容或多层陶瓷电容的高频特性较好。设计印刷线路板时,最好每个集成电路的电源,地之间都要加一个去耦电容。数字电路中典型的去耦电容为0.1μf的去耦电容有5nH分布电感,它的并行共振频率大约在7MHz左右,也就是说对于10MHz以下的噪声有较好的去耦作用,对40MHz以上的噪声几乎不起作用。1μf和10μf电容的并行共振频率在20MHz以上,去除高频率噪声的效果要好一些。在电源进入印刷板的地方和一个1μf或10μf的去高频电容往往是有利的,即使是用电池供电的系统也正在使用这种电容于其它用途。对微控制器构成的系统,去耦电容取0.01μf~0.1μf之间都可以。

在特定的场合下,两个并联电容可以提供更宽频带的射频抑制。为了获取最佳特性,这两个并联电容器必须相差两个量级幅度值(例如0.1μf和0.001μf)或100倍。在50MHz或者低于50MHz的系统下,最典型的高频去耦电容是0.1μf和0.001μf并联,在更高时钟频率下则为0.001μf和100pF并联。对于大规模集成电路,尤其是EPROM、FLASH MEMORY、EPLD、FPGA等类型的芯片,每个去耦电容旁要并接一个陶瓷电容。同时也也要注意会造成偏移原来中心工作频率的缺点。

在数字电路中,配置原则如下:

1)电源输入端一般跨接一个10μf~100μf的电解电容器,如果印制电路板的位置允许,采用100μf以上的电解电容器的抗干扰效果会更好。

2)为每个集成电路芯片配置一个陶瓷电容器。如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1μf~10μf钽电解电容器,这种器件的高频阻抗特别小,在500kHz~20MHz范围内阻抗小于1Ω,而且漏电流很小(0.5μA以下)。

3)对于噪声能力弱、关断时电流变化大的器件和ROM、RAM等存储型器件,应在芯片的电源线(Vcc)和地线(GND)间直接接入去耦电容。

3 去耦电容的摆放

尽量在关键元件,如ROM、RAM等芯片旁边安装去耦电容。防止Vcc走线上开关噪声尖峰的唯一方法,是在VCC与电源地之间安放一个0.1μf的电子去耦电容。如果电路板上使用的是表面贴装元件,可以用片状电容直接紧靠着元件,在Vcc引脚上固定,最好是使用瓷片电容。使去耦电容尽量靠近转换信号,去耦电容应连接到原始信号板下面的电源/接地面到新信号板下面的电源/接地面之间,如果这两种信号板下面的面均为接地面,则可以用通孔取代去耦电容。在安放去耦电容时需要注意以下几点:

1) 在印制电路板的电源输入端一般跨接一个电解电容,如果体积允许的话,电容量大一些则更好。

2) 原则上每个集成电路芯片的旁边都需要放置一个瓷片电容,如果电路板的空隙太小而放置不下时,可以每10个芯片左右放置一个1~10的钽电容。

3) 对于抗干扰能力弱、关断时电流变化大的元件和RAM、ROM等存储元件,应该在电源线(Vcc)和地线之间接入去耦电容。电容的引线不要太长,特别是高频旁路电容不能带引线。

4) 对于IC的电源,保证每个IC的电源PIN都有一个去耦电容,对于BGACHIP,要求在BGA的四角分别有两个电容共8个。对走线的电源尤其要注意加滤波电容,如VTT等。这不仅对稳定性有影响,对EMI也有很大的影响。

5) 对于时钟线的处理,如果时钟线有过孔,在过孔的相邻位置,地层和电源层之间加一个旁路电容,以确保时钟线换层后,参考层(相邻层)的高频电流的回路连续。旁路电容所在的电源层必须是过孔穿过的电源层,并尽可能地靠近过孔,旁路电容与过孔的间距最大不超过300MIL。

6) 时钟线下面没有铺铜。若条件限制实在做不到不穿孔,保证频率大于等于66M的时钟线不穿孔,频率小于66M的时钟线若穿孔,必须加一个去耦电容形成镜像通路。

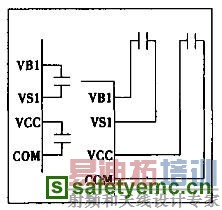

图2 某IC的去耦电容的位置

图3在模拟和数字PCB设计中,去耦或旁路电容(1mF)应尽量靠近器件放置。供电电源去耦电容(10mF)应放置在电路板的电源线入口处。所有情况下,这些电容的引脚都应较短。

图3 某IC的去耦电容的位置

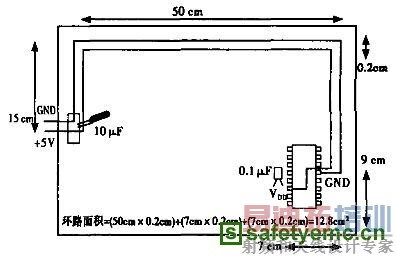

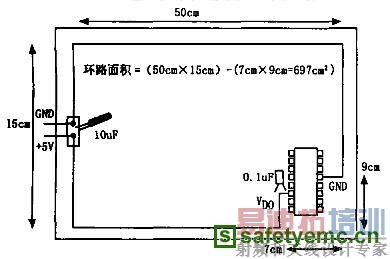

在安放跟去耦电容相匹配的电容时需注意电源线和地线的走线,由于这种不恰当的配合,电路板的电子元器件和线路受电磁干扰的可能性比较大。图4是不恰当的去耦电容布线。

图4 不恰当的去耦电容布线

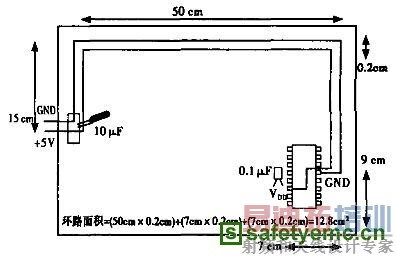

如果换成图5的走线方式,到电路板上电容的电源线和地线彼此靠近。此电路板中电源线和地线的配合比图4中恰当。电路板中电子元器件和线路受电磁干扰(EMI)的可能性降低了679/12.8倍或约54倍。

图5 恰当的去耦电容布线

4 小结

总之,去耦电容在PCD中的应用是解决高频高速信号频繁出现的有效方法之一,也是解决PCB的EMC设计问题的基本方法之一,要求选择合适的电容,合理安放,以提高信号质量。

参考文献

[1] 邝坚.华清远见CadencePCB初级设计[M].北京:清华大学出版社,2004.

[2] YorbeZhang.PCB的EMC设计[J].电子工程专辑,2005.

作者简介:张小行 江西蓝天学院电工电子教研室

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

上一篇:EMI/EMC设计讲座(六)

多层通孔和分离平面的概念

下一篇:EMI/EMC设计讲座(五)

映像平面的分割与隔离