- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

电路分享:基于FPGA的PCB测试机的设计

录入:edatop.com 点击:

硬件控制系统

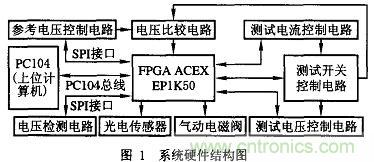

测试过程是在上位计算机的控制下,控制测试电路分别打开不同的测试开关。测试机系统由以下几部分构成: 上位计算机PC104 、测试控制逻辑(由FPGA 实现) 、高压测试电路。 其中上位机主要完成人机交互、测试算法、测试数据处理以及控制输出等功能。 FPGA 控制高压测试电路完成对PCB 的测试过程。

本系统以一台PC104 为上位计算机,以FPGA为核心,通过PC104 总线实现上位机对测试的控制。

测试系统总体框图如图1所示。

PC104总线是一种专为嵌入式控制定义的工业控制总线,其信号定义与ISA 总线基本相同。 PC104总线共有4 类总线周期,即8 位的总线周期、16 位的总线周期、DMA 总线周期和刷新总线周期。 16 位的I/O总线周期为3 个时钟周期,8 位的I/O总线周期为6 个时钟周期。 为了提高通信的速度,ISA总线采用16 位通信方式,即16 位I/O方式。 为了充分利用PC104的资源,应用PC104的系统总线扩展后对FPGA 进行在线配置。正常工作时通过PC104总线与FPGA进行数据通信。

FPGA与串行A/D及D/A器件的接口

根据测试机系统设计要求,需要对测试电压及两通道参考电压进行自检,即A/D转换通道至少有3 路。 两路比较电路的参考电压由D/A输出,则系统的D/A通道要求有两通道。 为了减少A/D及D/A的控制信号线数,选用串行A/D及D/A器件。 综合性能、价格等因素, 选用的A/D器件为TLC2543,D/A器件为TLV5618。

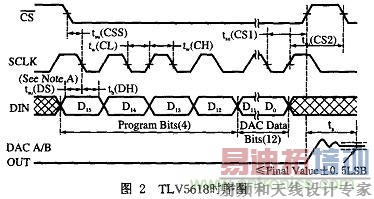

TLV5618是TI公司带缓冲基准输入(高阻抗)的双路12 位电压输出DAC,通过CMOS 兼容的3线串行总线实现数字控制。器件接收16 位命令字,产生两路D/A模拟输出。TLV5618只有单一I/O周期,由外部时钟SCL K决定,延续16 个时钟周期,将命令字写入片内寄存器,完成后即进行D/A转换。TLV5618读入命令字是从CS的下降沿开始有效,从下一SCLK的下降沿开始读入数据,读入16位数据后即进入转换周期,直到下次出现CS的下降沿。 其操作时序图如图2 所示。

[p]

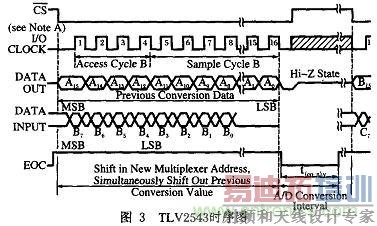

TLC2543是TI公司的带串行控制和11个输入端的12 位、开关电容逐次逼近型A/D转换器。 片内转换器有高速、高精度和低噪音的特点。 TLC2543工作过程分为两个周期:I/O周期和转换周期。I/O周期由外部时钟SCLK决定,延续8、12或16个时钟周期,同时进行两种操作: 在SCLK上升沿以MSB方式输入8位数据到片内寄存器;在SCLK下降沿以MSB 方式输出8、12、16位转换结果。转换周期在I/O周期的最后一个SCLK下降沿开始,直到EOC信号变高,指示转换完成。 为了与TLV5618的I/O周期一致,采用了MSB方式,使用CS的16 时钟传送的时序。其操作时序如图3 所示。

FPGA 程序框架

FPGA 片内程序是整个测试系统正确运行的关键。 由自顶向下的FPGA 设计原则,将系统分为5个独立的模块, 即通信模块(ISA) 、测试模块(TEST) 、AD/DA 模块、解码模块(DECODER) 、RAM 控制模块(RAMCTL)。

ISA 模块:系统通信及控制模块,完成与上位机通信、命令字解释、控制信号的产生等。系统根据上位机传送的导通电阻、绝缘电压等参数启动ADDA模块完成参考电压的输出;根据测试命令启动测试模块完成测试过程。数据在多个同步运行的同步状态机间传送,较难控制的是多进程间的数据通信与数据同步。

RAM控制模块:在测试开始前,上位机将测试点的信息通过总线传送至ISA模块, ISA 模块再将其存放到片内RAM中;测试完成后,将RAM中的测试结果传送到上位机。 在测试时测试模块通过读RAM中测试点的信息来打开相应测试开关,再将测试结果保存到RAM 中。 这样两个模块都要求读写RAM 以实现两个模块之间的数据共享,这就要求有一控制信号将两组读写信号线分别与RAM模块相连接,RAM控制模块即完成此功能。测试模块(TEST):虽然测试过程有多种,如开关卡自检、导通测试、绝缘测试等,但测试过程却是相同的,即测试扫描。 测试的工作过程是:加比较电路参考电压→打开待测点开关→延时→读比较器结果→测试另一组测试点。 本模块是按照不同的操作码,进入不同的测试过程。 测试结果与测试点编号一起组成13 位数据保存到RAM 中,并将原来测试点的编号信息覆盖。

解码模块(DECODER):这一模块挂在测试模块(TEST) 之后,它完成开关编号到实际电路的映射。 由于测试针阵形式不同、译码电路与控制电路的硬件设计不同,上级模块输出的测试开关信息并不能直接作为输出控制测试开关电路。 解码模块完成这两者间的转换。

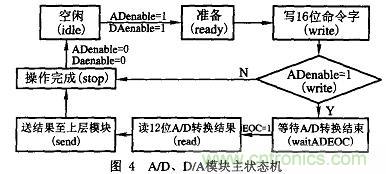

AD/DA 模块(AD/DA):设计SPI 总线接口对A/D 及D/A 器件操作,模块以允许(adenable , daenable) 信号启动,以busy信号作为转换完成标志信号,将A/D及D/A操作相对其它模块进行封装。系统的每个模块采用Verilog硬件描述语言编写,采用多个多层嵌套的同步状态机(FSM)完成整个系统的逻辑功能;每一模块应用仿真工具Modelsim完成模块的功能仿真,系统完成功能测试后;利用Altera 综合布线工具QuartusII完成系统后仿真及综合、布线、下载;充分利用Altera公司免费提供的IPcore 对程序模块进行优化;顶层设计采用方框图输入方式,模块间的数据流由方框图更直观地表现出来。

相关阅读:

PCB设计指导:如何改进高频信号传输中的SMT焊盘设计?

选择PCB元件的技巧从何谈起?那就从封装开始吧

PCB电路板为什么要做阻抗?意义何在

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...