- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

可怕的细节!PCB后期检查的六大要素

录入:edatop.com 点击:

很多初学者也包括一些有经验的工程师,由于时间紧或者不耐烦亦或者过于自信,往往草草了事,忽略了后期检查。结果出现了一些很基本的BUG,比如线宽不够,元件标号丝印压在过孔上,插座靠得太近,信号出现环路等等。从而导致电气问题或者工艺问题,严重的要重新打板,造成浪费。所以,当一块PCB完成了布局布线之后,很重要的一个步骤就是后期检查。

1、元件封装

(1)焊盘间距。如果是新的器件,要自己画元件封装,保证间距合适,焊盘间距直接影响到元件的焊接。

(2)过孔大小(如果有)。对于插件式器件,过孔大小应该保留足够的余量,一般保留不小于0.2mm比较合适。

(3)轮廓丝印。器件的轮廓丝印最好比实际大小要大一点,保证器件可以顺利安装。

2、布局

(1)IC不宜靠近板边。

(2)同一模块电路的器件应靠近摆放。比如去耦电容应该靠近IC的电源脚,组成同一个功能电路的器件优先摆放在一个区域,层次分明,保证功能的实现。

(3)根据实际安装安排插座的位置。插座都是引线到其他模块的,根据实际结构,为了安装方便,一般采用就近原则,安排插座的位置,而且一般靠近板边。

(4)注意插座方向。插座都是有方向的,方向反了,线材就要重新定做。对于平插的插座,插口方向应该朝向板外。

(5)Keep Out区域不能有器件。

(6)干扰源要远离敏感电路。高速信号、高速时钟或者大电流开关信号都属于干扰源,应该远离敏感电路,比如复位电路,模拟电路。可以用铺地来隔开它们。

3、布线

(1)线宽大小。线宽要结合工艺、载流量来选择,最小线宽不能小于PCB厂家的最小线宽。同时保证承载电流能力,一般以1mm/A来选取合适线宽。

(2)差分信号线。对于USB、以太网等差分线,注意走线要等长、平行、同平面,间距由阻抗决定。

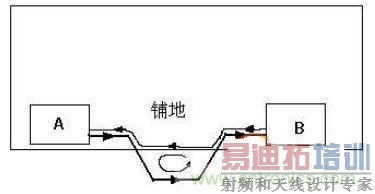

(3)高速线注意回流路径。高速线容易产生电磁辐射,如果走线路径与回流路径形成面积过大,就会形成一个单匝线圈向外辐射电磁干扰,如图1。所以走线的时候要注意旁边有回流路径,多层板设置有电源层和地平面可以有效解决这个问题。

(4)注意模拟信号线。模拟信号线应该与数字信号隔开,走线尽量避免从干扰源(如时钟、DC-DC电源)旁边走过,而且走线越短越好。

图1

(1)端接电阻。高速线或者频率较高并且走线较长的数字信号线最好在末端串入一个匹配电阻。

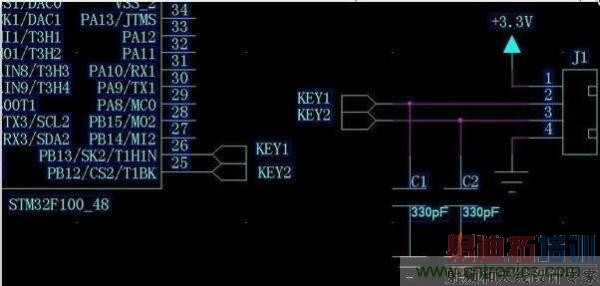

(2)输入信号线并接小电容。从接口输入的信号线,最好在靠近接口的地方并接皮法级小电容。电容大小根据信号的强度以及频率决定,不能太大,否则影响信号完整性。对于低速的输入信号,比如按键输入,可以选用330pF的小电容,如图2。

图2

5、丝印

(1)板名、时间、PN码。

(2)标注。对一些接口(如排阵)的管脚或者关键信号进行标注。

(3)元件标号。元件标号要摆放至合适的位置,密集的元件标号可以分组摆放。注意不要摆放在过孔的位置。

6、其他

最后要说的就是Mark点。我们对于需要机器焊接的PCB,需要加入两到三个的Mark点。

相关阅读:

PCB设计指南:关于射频走线和地的那些事

影响PCB价格的诸多因素,可怕的是大家都忽略了

电容的容值选择及Fanout设计(下)-PCB设计的十大误区

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...