- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高频电路PCB设计必知:阻抗控制和叠层设计

随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB 迹线不再是简单的连接,而是传输线。

在实际情况中,需要在数字边际速度高于1ns或模拟频率超过300Mhz时控制迹线阻抗。PCB 迹线的关键参数之一是其特性阻抗(即波沿信号传输线路传送时电压与电流的比值)。印制电路板上导线的特性阻抗是电路板设计的一个重要指标,特别是在高频电路的PCB设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。这就涉及到两个概念:阻抗控制与阻抗匹配,本文重点讨论阻抗控制和叠层设计的问题。

阻抗控制。

阻抗控制(eImpedance Controling),线路板中的导体中会有各种信号的传递,为提高其传输速率而必须提高其频率,线路本身若因蚀刻,叠层厚度,导线宽度等不同因素,将会造成阻抗值得变化,使其信号失真。故在高速线路板上的导体,其阻抗值应控制在某一范围之内,称为“阻抗控制”。

PCB 迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。影响PCB走线的阻抗的因素主要有: 铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。PCB 阻抗的范围是 25 至120 欧姆。

在实际情况下,PCB 传输线路通常由一个导线迹线、一个或多个参考层和绝缘材质组成。迹线和板层构成了控制阻抗。PCB 将常常采用多层结构,并且控制阻抗也可以采用各种方式来构建。但是,无论使用什么方式,阻抗值都将由其物理结构和绝缘材料的电子特性决定:

信号迹线的宽度和厚度

迹线两侧的内核或预填材质的高度

迹线和板层的配置

内核和预填材质的绝缘常数

PCB传输线主要有两种形式:微带线(Microstrip)与带状线(Stripline)。

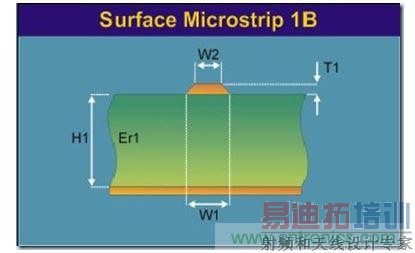

微带线(Microstrip):

微带线是一根带状导线,指只有一边存在参考平面的传输线,顶部和侧边都曝置于空气中(也可上敷涂覆层),位于绝缘常数 Er 线路板的表面之上,以电源或接地层为参考。如下图所示:

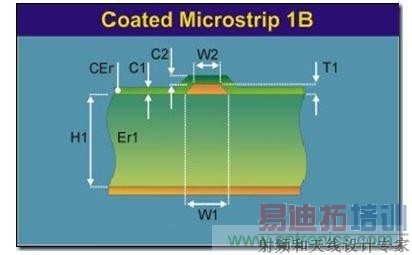

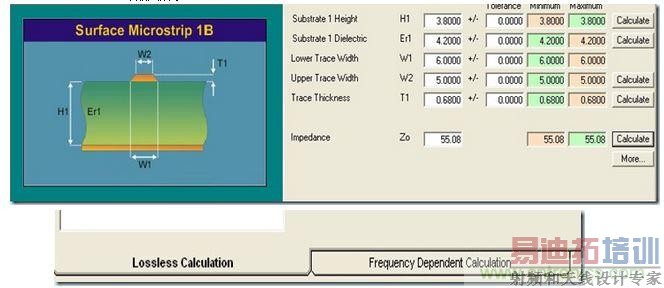

注意:在实际的PCB制造中,板厂通常会在PCB板的表面涂覆一层绿油,因此在实际的阻抗计算中,通常对于表面微带线采用下图所示的模型进行计算:

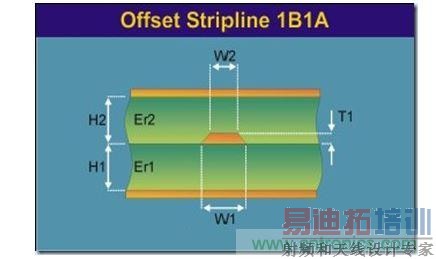

带状线(Stripline):

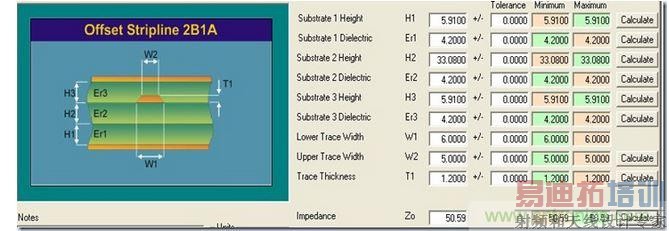

带状线是置于两个参考平面之间的带状导线,如下图所示,H1和H2代表的电介质的介电常数可以不同。

上述两个例子只是微带线和带状线的一个典型示范,具体的微带线和带状线有很多种,如覆膜微带线等,都是跟具体的PCB的叠层结构相关。

用于计算特性阻抗的等式需要复杂的数学计算,通常使用场求解方法,其中包括边界元素分析在内,因此使用专门的阻抗计算软件SI9000,我们所需做的就是控制特性阻抗的参数:

[p]绝缘层的介电常数Er、走线宽度W1、W2(梯形)、走线厚度T和绝缘层厚度H。

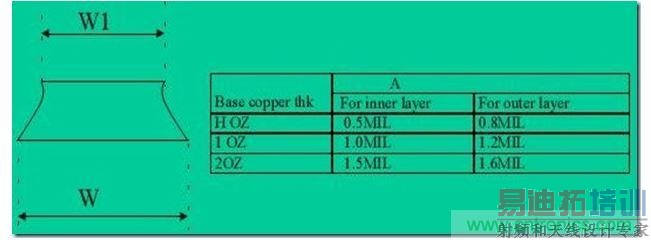

对于W1、W2的说明:

此处的W=W1,W1=W2.

规则:W1=W-A

W—-设计线宽

A—–Etch loss (见上表)

走线上下宽度不一致的原因是:PCB板制造过程中是从上到下而腐蚀,因此腐蚀出来的线呈梯形。

走线厚度T与该层的铜厚有对应关系,具体如下:

铜厚

COPPER THICKNESS

Base copper thk For inner layer For outer layer

H OZ 0.6mil 1.8mil

1 OZ 1.2MIL 2.5MIL

2 OZ 2.4MIL 3.6MIL

绿油厚度:

*因绿油厚度对阻抗影响较小,故假定为定值0.5mil。

我们可以通过控制这几个参数来达到阻抗控制的目的,下面以安维的底板PCB为例说明阻抗控制的步骤和SI9000的使用:

底板PCB的叠层为下图所示:

第二层为地平面,第五层为电源平面,其余各层为信号层。

各层的层厚如下表所示:

Layer Name Type Material Thinkness Class

SURFACE AIR

TOP CONDUCTOR COPPER 0.5 OZ ROUTING

DIELECTRIC FR-4 3.800MIL

L2-INNER CONDUCTOR COPPER 1 OZ PLANE

DIELECTRIC FR-4 5.910MIL

L3-INNER CONDUCTOR COPPER 1 OZ ROUTING

DIELECTRIC FR-4 33.O8MIL

L4-INNER CONDUCTOR COPPER 1 OZ ROUTING

DIELECTRIC FR-4 5.910MIL

L5-INNER CONDUCTOR COPPER 1 OZ PLANE

DIELECTRIC FR-4 3.800MIL

BOTTOM CONDUCTOR COPPER 0.5 OZ ROUTING

SURFACE AIR

说明:中间各层间的电介质为FR-4,其介电常数为4.2;顶层和底层为裸层,直接与空气接触,空气的介电常数为1。

[p]需要进行阻抗控制的信号为:

DDR的数据线,单端阻抗为50欧姆,走线层为TOP和L2、L3层,走线宽度为5mil。

时钟信号CLK和USB数据线,差分阻抗控制在100欧姆,走线层为L2、L3层,走线宽度为6mil,走线间距为6mil。

对于计算精度的说明:

1、对于单端阻抗控制,计算值等于客户要求值;

2、对于其他特性阻抗控制:

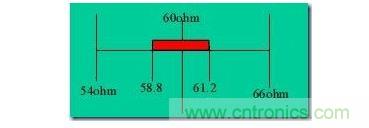

对于其它所有的阻抗设计(包括差别和特性阻抗)

*计算值与名义值差别应小于的阻抗范围的10%:

例如:客户要求:60+/-10%ohm

阻抗范围=上限66-下限54=12ohms

阻抗范围的10%=12X10%=1.2ohms

计算值必须在红框范围内。其余情况类推。

下面利用SI9000计算是否达到阻抗控制的要求:

首先计算DDR数据线的单端阻抗控制:

TOP层:铜厚为0.5OZ,走线宽度为5MIL,距参考平面的距离为3.8MIL,介电常数为4.2。选择模型,代入参数,选择lossless calculation,如图所示:

计算得到单端阻抗为Zo=55.08ohm,与要求相差5欧姆。根据板厂的反馈,他们将走线宽度改为6MIL以达到阻抗控制,经过验证,在宽度W2=6MIL,W1=7MIL的情况下,计算得到的单端阻抗为Zo=50.56欧姆,符合设计要求。

L2层:在L2层的走线模型如下图所示:

代入参数进行计算得到如下图所示:

计算得到单端阻抗为Zo=50.59欧姆,符合设计要求。

同理可以得到L3层的单端阻抗,在此不再赘述。

[p]下面计算差分阻抗控制:

由PCB设计可知,底板PCB中时钟走线在L3层,USB数据线在L2层,走线宽度均为6MIL,间距为6MIL。

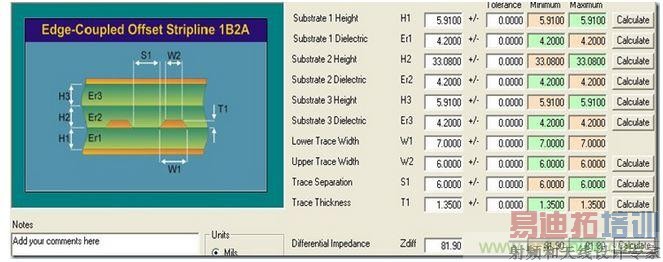

时钟信号选择的模型如下所示:

按照提供给板厂的数据计算得到的结果如下图所示:

根据板厂的反馈,差分阻抗只能做到85欧姆,与计算结果接近(他们可以微调板层厚度,但不能调线)。但是改变线间距为12MIL时,计算得到的差分阻抗为92.97欧姆,再将线宽调为5MIL时,差分阻抗为98.99欧姆,基本符合设计要求。

经验小结

1、当差分走线在中间信号层走线时,差分阻抗的控制比较困难,因为精度不够,就是说改变介质层厚度对差分阻抗的影响不大,只有改变走线的间距才对差分阻抗影响较大。但是当走线在顶层或底层时,差分阻抗就比较好控制,很容易达到设计要求,通过实际计算发现,重要的信号线最好走表层,容易进行阻抗控制,尤其是时钟信号差分对。

2、在PCB设计之前,首先必须通过阻抗计算,把PCB的叠层参数确定,如各层的铜厚,介质层的厚度等等,还有差分走线的宽度和间距都需要事先计算得出,这些就是PCB的前端仿真,保证重要的信号线的阻抗控制满足设计要求。

3、关于介电常数Er的问题:

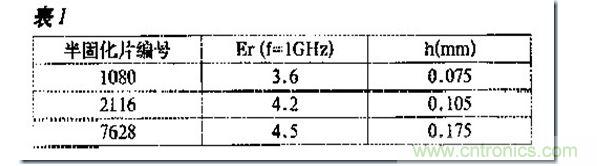

以我们使用最多的FR-4介质的材料板为例:实际多层板是芯板和压合树脂层堆叠而成,其芯板本身也是由半固化片组合而成。常用的三种半固化片技术指标如下表1 所示。

半固化片组合的介电常数不是简单的算术平均,甚至在构成微带线和带状线时的Er值也有所不同。另一方面,FR-4的Er也随信号频率的变化有一定改变,不过在1GHz 以下一般认为FR-4 材料的Er 值约4.2。通常计算时采用4.2。

4、在实际的阻抗控制中,一般采用介质为FR-4,其Er约4.2,线条厚度t对阻抗影响较小,实际主要可以调整的是H和W,W(设计线宽)一般情况下是 由设计人员决定的,但在设计时应充分考虑线宽对阻抗的配合性和实际加工精度。当然,采用较小的W 值后线条厚度t 的影响就不容忽视了。H(介质层厚度)对阻抗控制的影响最大,实际H 有两类情况:一种是芯板,材料供应商所提供的板材中H的厚度也是由以上三种半固化片组合而成,但其在组合的过程中必然会考虑三种材料的特性,而绝非无条件 的任意组合,因此板材的厚度就有了一定的规定,形成了一个相应的清单,同时H 也有了一定的限制。如0.17mm 1/1的芯板为 2116 ×1,0.4mm 1/1的芯板为1080×2+7628×1等。另一种是多层板中压合部分的厚度:其方法基本上与前相同但需注意铜层的损失。如内电层间用半固化片进行填 充,因在制作内层的过程中铜箔被蚀刻掉的部分很少,则半固化片中树脂对该区的填充亦很少,则半固化片的厚度损失可忽略。反之,如信号层之间用半固化片进行 填充,由于铜箔被蚀刻掉的部分较多,则半固化片的厚度损失会很大且难以估计。因此,有人建议在内层的信号层要求铺铜以减少厚度损失。

5、特征阻抗与传输线的宽度是成反比的,宽度越宽,阻抗越低,反之则阻抗更高。

6、在有些板的设计要求中对板层厚度有限制时,此时要达到比较好的阻抗控制,采用好的叠层设计非常关键。从实际的计算中可以得出以下结论:

a. 每个信号层都要有参考平面相邻, 能保证其阻抗和信号质量;

b. 每个电源层都要有完整的地平面相邻, 使得电源的性能得以较好的保证;

[p]7、关于差分走线的线宽和间距对阻抗控制的讨论:

通过软件计算发现,改变差分对的间距对阻抗控制的影响较大,但是这里涉及到另一个问题,就是差分对的耦合问题。

差分对耦合的主要目的是增强对外界的抗干扰能力和抑止EMI。耦合分为紧耦合方式( 即差分对线间距小于或等于线宽) 和松耦合方式。

如果能保证周围所有的走线离差分对较远(比如远远大于3 倍的线宽),那么差分走线可以不用保证紧密的耦合,最关键的是保证走线长度相等即可。(可以参见Johnson 的信号完整性网站上的关于差分走线的阐述,他就要求他的layout 工程师将差分线离得较远,这样可以方面绕线)。只是目前大多数多层高速的PCB 板走线空间很紧密,根本无法将差分走线和其它走线隔离开来,所以这时候保持紧密的耦合以增加抗干扰能力是应该的。

紧耦合不是差分走线的必要条件,但是在空间不够时走线采用紧耦合方式能够增强差分走线的抗干扰能力。因此,对于差分对的阻抗控制问题,怎么调节各个参数需要综合考虑上述因素,择优选择。一般情况下不轻易调整差分对的间距和线宽。

延伸:差分对走线的PCB要求

(1)确定走线模式、参数及阻抗计算。差分对走线分外层微带线差分模式和内层带状线差分模式两种,通过合理设置参数,阻抗可利用相关阻抗计算软件(如POLAR-SI9000)计算也可利用阻抗计算公式计算。

(2)走平行等距线。确定走线线宽及间距,在走线时要严格按照计算出的线宽和间距,两线间距要一直保持不变,也就是要保持平行。平行的方式有两种: 一种为两条线走在同一线层(side-by-side),另一种为两条线走在上下相两层(over-under)。一般尽量避免使用后者即层间差分信号, 因为在PCB板的实际加工过程中,由于层叠之间的层压对准精度大大低于同层蚀刻精度,以及层压过程中的介质流失,不能保证差分线的间距等于层间介质厚度, 会造成层间差分对的差分阻抗变化。困此建议尽量使用同层内的差分。

(3).紧耦合原则。

在计算线宽和间距时最好遵守紧耦合的原则,也就是差分对线间距小于或等于线宽。当两条差分信号线距离很近时,电流传输方向相反,其磁场相互抵消,电场相互耦合,电磁辐射也要小得多。

(4).走短线、直线。

为确保信号的质量,差分对走线应该尽可能地短而直,减少布线中的过孔数,避免差分对布线太长,出现太多的拐弯,拐弯处尽量用45°或弧线,避免90°拐弯。

(5).不同差分线对间处理。

差分对对走线方式的选择没有限制,微带线和带状线均可,但是必须注意要有良好的参考平面。对不同差分线之间的间距要求间隔不能太小,至少应大于3~5倍差分线间距。必要时在不同差分线对之间加地孔隔离以防止相互问的串扰。

(6).远离其它信号。

对差分对信号和其它信号比如TTL信号,最好使用不同的走线层,如果因为设计限制必须使用同一层走线,差分对和TTL的距离应该足够远,至少应该大于3~5倍差分线间距。

(7).差分信号不可以跨平面分割。

尽管两根差分信号互为回流路径,跨分割不会割断信号的回流,但是跨分割部分的传输线会因为缺少参考平面而导致阻抗的不连续(如图箭头处所示,其中GND1、GND2为LVDS相邻的地平面)。

8、PADS LAYOUT中层定义选项卡各个参数的解释说明:

coating表示涂覆层,如果没有涂覆层,就在thickness 中填0,dielectric(介电常数)填1(空气)。

substrate表示基板层,即电介质层,一般采用FR-4,厚度是通过阻抗计算软件计算得到,介电常数为4.2(频率小于1GHz时)。

点击Weight(oz)项,可以设定铺铜的铜厚,铜厚决定了走线的厚度。

9、绝缘层的Prepreg/Core的概念:

PP(prepreg)是种介质材料,由玻璃纤维和环氧树脂组成,core其实也是PP类型介质,只不过他的两面都覆有铜箔,而PP没有,制作多层板时,通常将CORE和PP配合使用,CORE与CORE之间用PP粘合。

10、PCB叠层设计中的注意事项:

(1)、翘曲问题

PCB的叠层设计要保持对称,即各层的介质层厚、铺铜厚度上下对称,拿六层板来说,就是TOP-GND与BOTTOM-POWER的介质厚度和铜厚一致,GND-L2与L3-POWER的介质厚度和铜厚一致。这样在层压的时候不会出现翘曲。

(2)、信号层应该和邻近的参考平面紧密耦合(即信号层和邻近敷铜层之间的介质厚度要很小);电源敷铜和地敷铜应该紧密耦合。

(3)、在很高速的情况下,可以加入多余的地层来隔离信号层,但建议不要多家电源层来隔离,这样可能造成不必要的噪声干扰。

(4)、典型的叠层设计层分布如下表所示:

(5)、层的排布一般原则:

元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;

所有信号层尽可能与地平面相邻;

尽量避免两信号层直接相邻;

主电源尽可能与其对应地相邻;

兼顾层压结构对称。

对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在50MHZ 以上的(50MHZ 以下的情况可参照,适当放宽),建议排布原则:

元件面、焊接面为完整的地平面(屏蔽);

无相邻平行布线层;

所有信号层尽可能与地平面相邻;

关键信号与地层相邻,不跨分割区。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...