- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

专家讲解:高速信号仿真之IBIS

而对于初学仿真的小伙伴们,则可能从学习传输线开始,需要了解高速信号是怎么传输的,要学习反射,串扰,端接,匹配,损耗……然而,当我们真正准备仿真一个DDR信号质量时,却是从学会调用IBIS模型开始的。

我们在接到仿真项目时,总是免不了要向客户索要芯片模型。俗话说:巧妇难为无米之炊。没有米,是不可能做出香喷喷的米饭的,没有准确的芯片模型,我们的仿真就无法进行。 在仿真分析中,最常见的模型就是IBIS模型了。小编这篇文章不是要介绍怎么去使用IBIS,也不是要去阐述 IBIS是怎么得来的,只是先让初学者对IBIS有一个感性的认识。

进入正题。我们知道IBIS模型是行为级模型,它描述了芯片的输入输出状态,它不同于Spice模型,不会泄露芯片内部的电路结构。

首先,让我们来思考一下仿真分析为什么需要IBIS模型。

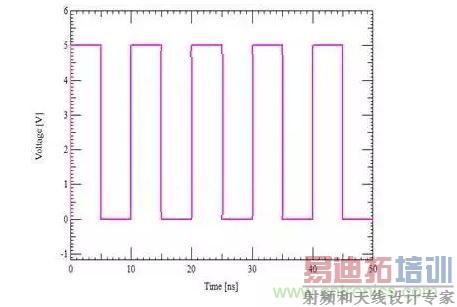

从根源说起。在数字电路中,芯片与芯片之间传输的是数字信号,数字信号是0、1这样的脉冲信号。完美的数字信号应该是图一这样的,它的上升时间和下降时间几乎为零

图一

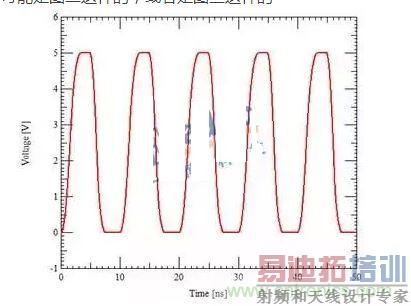

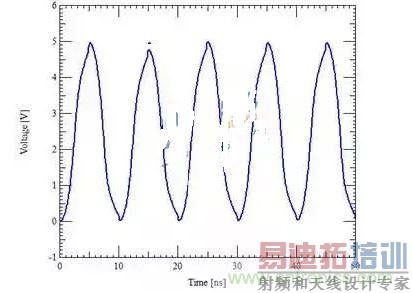

但实际传输的信号,可能是图二这样的,或者是图三这样的

图 三

我们可以看到,上图这些信号都是幅值为5V的脉冲,频率为100M,但是它们的特点不一样。图二波形的上升沿很陡峭,图三波形的上升沿却很平缓。

实际应用中,我们使用的芯片也是这样,不同芯片输出的波形也不一样。它们不仅周期频率不同,上升时间、幅值也会不同。

先来了解一下芯片的构造。看来做为一名SI工程师,需要学习和掌握的东西还真不少。不光是关注传输线外部互连,还需要学习很多芯片知识。

我们姑且认为IC芯片由三部分组成: Core、Buffer和封装。Core是芯片内部的核心逻辑电路,工作电压较低,驱动能力也低。Buffer是终端接口电路,电源电压一般较高,驱动能力较强,是core和其他IC之间的连接桥梁,封装则是连接Buffer和外部器件的金线和管脚。芯片核心与核心之间的通信就是通过buffer、封装和传输线来完成的。Buffer和封装是外围电路能“看见”的部分。就是说芯片内的指令是由core来发出的,至于指令是以什么形式,以多高的电压来表现,这就要看 Buffer来发挥作用了。

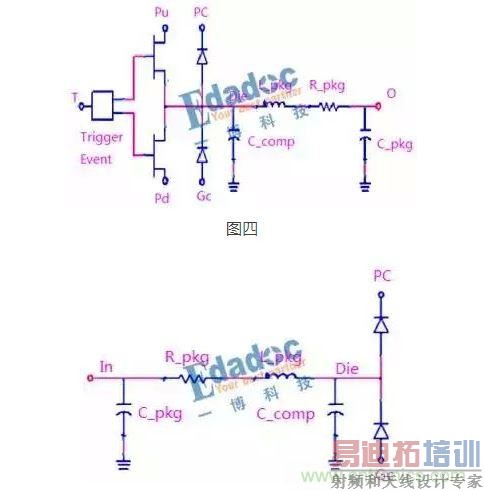

说到Buffer,那么Buffer究竟是什么呢?就像传输线可以用分布模型RLGC来定义,Buffer也可以用一些等效电路来描述。IBIS里面的Buffer有Input Buffer,Output Buffer,Input/Output Buffer等类型。

[p]下图就是Buffer和封装的等效电路,图四是Output buffer,图五是Input Buffer。这里要强调一下,下图是包含了Buffer和封装的,图四右边部分是封装等效电路。图五左边部分是封装等效电路。我们需要明白的是IBIS模型是考虑了封装的影响的。小编的模电学的不是很好,不想去详细分析这些器件是怎么工作的。

图五

那么仿真时调用不同的IBIS模型有什么区别呢?我们调用实际的IBIS模型来仿真一下,看看仿真时调用不同的IBIS模型之间到底有什么区别。

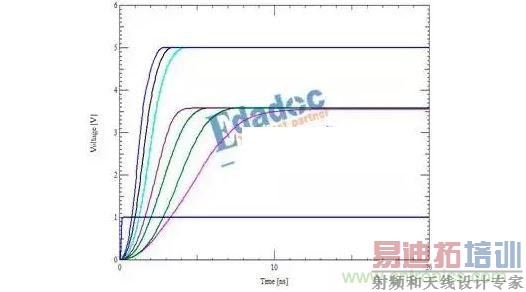

首先来挑选几个不同的IBIS模型,加载一个上升沿,输出的结果如图六:

图六

上图这些上升沿的上升边陡峭程度不一样,对应的幅值也不一样。可见,调用不同的模型,同样是一个上升沿,会有这么多的表现形式。

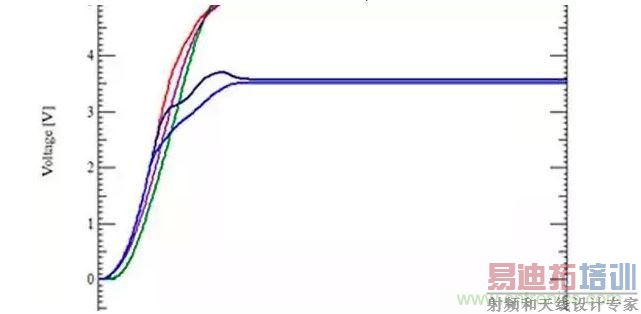

我们再来看看接收端模型对信号有什么影响。驱动端加载一个上升沿,输入到输出之间的线很短,可以忽略传输线对信号的影响。终端调用了不同的Input模型,结果如下图七。

图七

仿真时,驱动端加载的是5V上升沿信号。接收端接收的电压有5V,3.3V。同样的输入,但是在终端接收的电压不一样。对于供电电压是3.3V的接收端器件,就算驱动电压是5V,它也会在保护二极管的作用下,最终电压被拉回到3.3V。而对于供电电压本来就是5V的器件,调用不同的Input buffer模型对信号波形的影响是比较小的。这里我们就明白了,为什么在仿真中,如果我们不能准确找到接收芯片模型,可以用类似的模型去替代。

通过仿真我们了解到,Buffer本身并不能产生信号波形,它本身是个被动器件,只是起驱动的作用。我们在仿真的时候自己会定义各种码型,码型只是定义一种逻辑关系而已,至于这种逻辑关系是以什么形式表现出来,就要看芯片的Buffer了。在仿真中,我们想要知道主控芯片输出的波形长什么样,那就要借助我们的IBIS模型了。

以上是我对IBIS模型的一点认识,欢迎讨论。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...