- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

噪声问题复杂化的因素

录入:edatop.com 点击:

在此之前,已经通过较为简单的表述解释了噪声的产生(谐波除外)。但是,在解释噪声传输和发射的机制时,会提及传输理论、电磁学和天线理论中使用的术语(如图1所示)。如果不理解这些术语,就无法处理噪声问题。

因此,本文将(尽量使用较少的公式)解释这些术语,并介绍关于噪声的重要课题,如谐振和阻尼、噪声传导和反射以及源阻抗。

图1 将要介绍的内容

谐振和阻尼

在产生噪声或接收到噪声感应时,谐振是一个重要因素。如果电路中包含意外建立的谐振电路,则会在谐振频率处产生非常大的电流或电压,更易产生噪声干扰。尽可能消除电路中的谐振是很重要的。如果要抑制谐振,需使用阻尼电阻器。本章节将介绍谐振和阻尼电阻器。

并联谐振和串联谐振

(1) LC谐振电路

谐振指的是电路中的感应电抗和电容电抗在特定频率处相互抵消,这个特定频率就叫做“谐振频率”。尽管能产生电抗(阻抗的虚数分量)的典型元件是电感 器 (线圈) 和电容器,但任何其他元件,甚至连简单的导线都可以是产生谐振的要素,因为它们仍具有非常小的电抗。(尽管除上述元件之外,天线、平行板、传输路径等也可 能导致与EMC相关的谐振,但此处我们只着重于电感器和电容器产生的LC谐振。)

(2) 谐振电路的阻抗

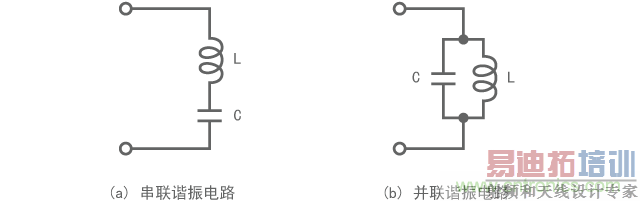

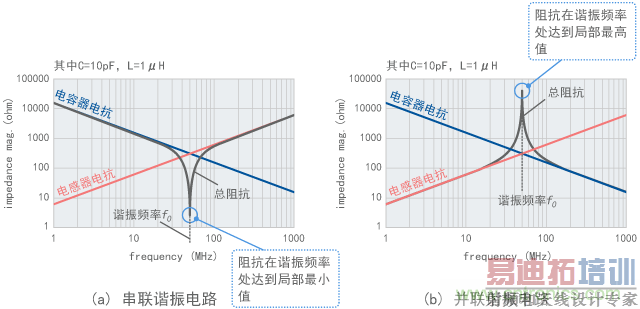

如图2所示,谐振电路分两种: 串联谐振和并联谐振。根据图3中的计算示例,串联谐振使阻抗降至最低值(理论上为零),而并联谐振使阻抗升到最高值(理论上为无穷大)。

图2 串联谐振和并联谐振

(该图表示电抗在数轴上的大小)

图3 谐振电路的阻抗

(3) 电抗抵消为零

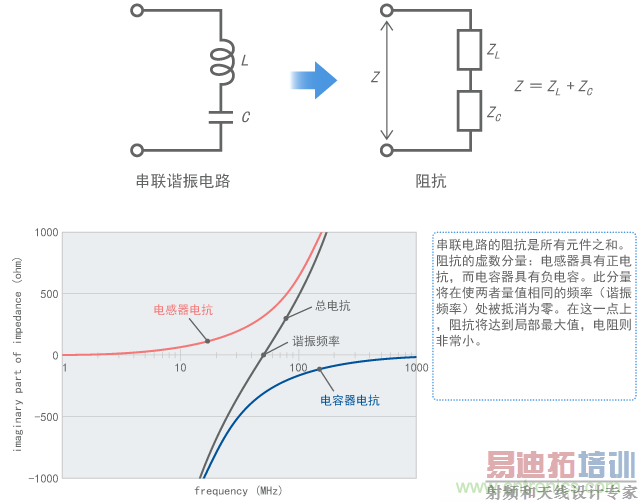

如图4所示,电感器电抗和电容器电抗的量值在谐振频率处变为相等,两者相互抵消,最终相加之和为零。

图4解释了串联谐振的情形;如果是并联谐振,则将电抗替换为电纳(导纳的虚数成分),会出现电纳在谐振频率处被抵消为零。因此,阻抗升到最高值,这很容易理解。 [p]

(4) 谐振频率

无论是串联谐振还是并联谐振,都可以通过以下公式估算出谐振频率ƒ0。在图3的示例中,ƒ0约为50MHz。

(公式1)

(5) 谐振Q

谐振强度可通过指数Q(质量因子)来表示。Q越高表示谐振越强。指数Q也是用作表示电容器和电感器性能的指数。存在这样一种关系: 当使用Q值较大的电容器或电感器时,所建立谐振电路的Q值也较大。如何估算Q值将在章节3-2-5中作解释。

(6) 电容器和电感器的自谐振

在高频范围内使用电容器或电感器时,由于其固有的寄生成分,电容器或电感器本身会在特定频率处导致谐振。这就叫做自谐振。自谐振将在第6章中进一步讲述。

图4 串联谐振使阻抗降至最低值的机制

[p] 关于谐振电路EMC措施的问题

(1) 谐振电路放大电压

如果电路中存在意外产生的谐振,阻抗会在谐振频率处发生显著变化,导致较大的电流或电压,这会是产生噪声干扰的一个原因。

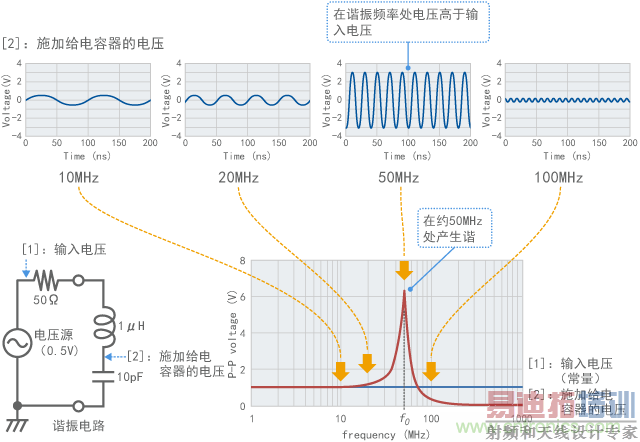

例如,从外侧向图3(a)中计算的串联谐振电路输入交流信号。如图5所示,当使用输出阻抗为50Ω的信号发生器施加电压恒定(振幅0.5V)的信号时,电容器会在50MHz谐振频率处产生比输入信号高数倍的电压。在这种情况下,电容器或电感器上产生的电压达到输入电压与Q的乘积。如何估算Q值将在章节3-2-5中作解释。图5的的情况表明Q = 6.3。

(2) 谐振电路可能意外产生

图5中的测试电路包括一个电容器和一个电感器,其中使用的常数为数字电路中通常会产生的值。例如,数字IC的输入端子具有不同pF的浮动静 电容量。线路的电感约为1uH/米。因此,如果将约1m的电缆连接至数字IC的输入端子(将其连接至外部传感器等),就会产生此处所示的谐振电路。

如果误将导体连接至此点,就会成为噪声发射的原因之一。

图5 谐振电路的频率特征示例(计算值)

(3) 在输入电压很小的情况下内部电压升高

如图3(a)所示,串联谐振电路的阻抗在谐振频率处达到最低值。因此,您可能简单地认定电压降低。但实际上电压为什么会升高呢?

图6显示了电压的分解。谐振电路入口处(电阻器和电感器的中点)处的电压确实降低到非常小的水平。但是,由于阻抗降低,电流变大了。因此,谐振电路内产生了比所施加电压更高的电压。

在电容器接收一定电压时,为什么谐振电路入口处的电压会消失?此时,电感器也像电容器一样,接收了完全相同的电压。因为此电压的方向与电容器电压的方向相反,所以在谐振电路入口处几乎察觉不到任何电压。 [p]

(4) 谐振电路各点的电压完全不同

当电路发生谐振时,电路各点的电压相差很大。即使某点的电压测量值似乎表明噪声有所减弱,但整个噪声发射的测量值也可能保持不变甚至有所升高。所以需要注意这样的情况。

上面的例子是关于串联谐振电路的情形。如果是并联谐振电路,流经电容器和电感器的电流会比输入信号的电流更高。因为这种电流也是产生噪声的原因之一,所以在并联谐振电路的情况下也需要注意。

数字电路连接至谐振电路时

(1) 在谐振频率处更容易产生噪声

如上所述,如果将可以作为天线的导体连接至谐振电路,导体会接收谐振频率的高压,产生很强的发射,从而导致噪声。此外,就抗扰度而言,噪声容易在谐振频率处被接收。

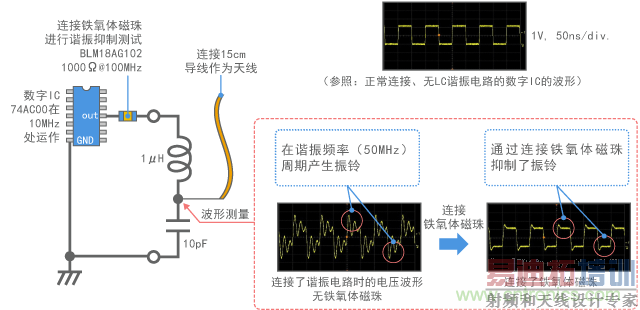

如果接有天线的谐振电路连接至包含很宽范围频率的信号(如数字信号),谐振频率附近频率的谐波将具有很强的发射性。图7和图8给出了一些 例子: 在上述50MHz串联谐振电路连接至10MHz时钟脉冲信号时,测量脉冲波形和发射的变化。作为噪声抑制的示例,图中也指出了连接有铁氧体磁珠时的波形和 发射。

(2) 数字信号连接至谐振电路时

图7提供了测试电路及电压波形的测量结果。作为噪声源的数字IC中使用了74AC00。IC的输出端连接至谐振频率为50MHz的串联谐振 电路。观察到的波形表明10MHz数字脉冲中存在强烈的振铃,使脉冲波形严重失真。这是因为,在10MHz信号所包含的谐波中,仅提取了第5次谐波 (50MHz)。(观察到振铃频率为50MHz) [p]

(3) 使用铁氧体磁珠的阻尼

后面将会介绍阻尼电阻器和铁氧体磁珠能有效抑制这类谐振。图7展示了连接有铁氧体磁珠时的波形。从图中可以发现,谐振已经得到抑制,信号也恢复到原来的脉冲波形。

(4) 通过噪声发射确认谐振

图8显示了噪声发射的结果。磁场强度是通过“3米法”测量的。为便于参照,图中也提供了无天线情况下的测量结果,而且已经证实了在仅包括数字IC和谐振电路时,几乎没有噪声发射。图中下部的曲线表示频谱分析仪的黑色噪声电平。

(5) LC谐振和天线谐振

图8(a)指出了用15cm导线作为天线连接谐振电路来发射噪声的情形。在LC谐振电路的谐振频率50MHz处观察到强烈的发射。除了此频 率外,还在500MHz处观察到了噪声。在该频率处,作为天线连接的15cm导线作为1/4波长天线工作。因此,除了图8(a)中的LC谐振,还 可能观察到天线的谐振效应。天线的谐振将在后续章节中进行讲述。

图8(b)显示了连接铁氧体磁珠时的测量结果。可以发现噪声发射得到了有效抑制。

图7 谐振电路和天线连接至数字信号的测试电路

图8 谐振电路和天线连接至数字信号时的噪声发射

[p] 无电感器或电容器的情况下产生谐振的示例

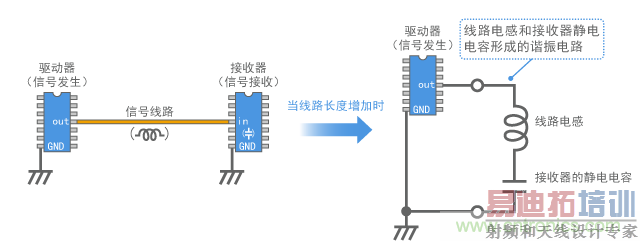

(1) 数字信号线建立的谐振电路

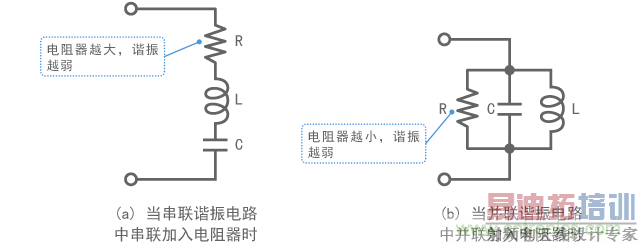

为了进行测量并着重考察图7和图8中的谐振效应,试验中使用了电容器和电感器建立LC谐振电路。但是,在实际电路中,没有这些元件也会产生谐振。

例如,在如图9所示的数字信号线路中,驱动器和接收器之间连接的导线存在电感。此外,接收信号的接收器的输入端存在静电容量。

(2) 随着谐振频率降低问题变得明显

当数字信号线路非常短时,这些因素导致的谐振频率会变得非常高(100MHz以上),因此其影响可以忽略。但是,如果使用的是双面板,或通过延长线路增强电感,或通过连接多个接收器增加静电容量,较低谐振频率产生的影响(脉冲波形失真或噪声发射增强等)将不可忽略。

为应对上述情形,可为信号输出元件提供连接盘,便于使用诸如铁氧体磁珠的谐振抑制元件,从而能够按照章节7所述轻松实施噪声抑制措施。

图9 数字信号线路构建的谐振电路模型

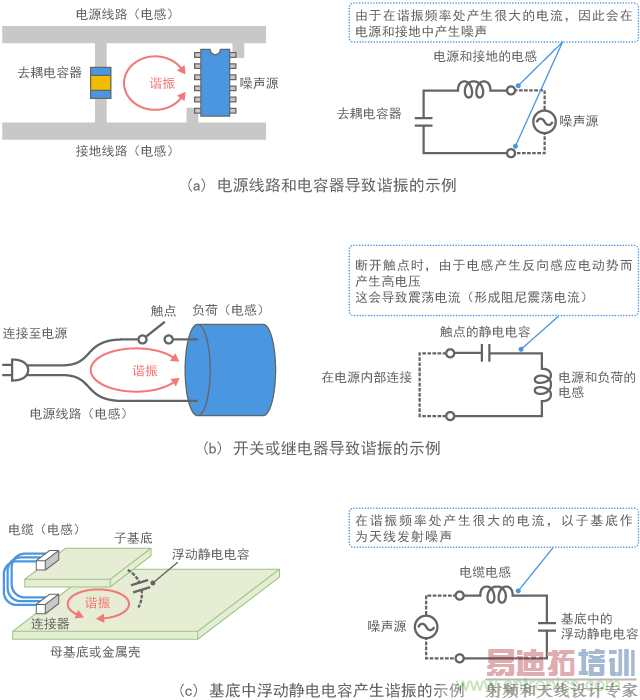

(3) 电源电缆和印刷电路板可能是产生谐振的原因

除了数字信号外,各种构成电路的因素都可作为电路图中未提及的电容器或电感器运作,并导致谐振。所以需要注意这样的情况。图10提供了一个示例。

图10 谐振示例

[p] 电阻器及铁氧体磁珠的阻尼作用(1) 串联谐振电路的阻尼

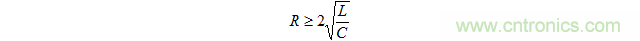

可通过在谐振电路中加入电阻器来抑制谐振。这种电阻器被称为阻尼电阻器。图11提供了增加阻尼电阻器的一个示例(在图中表示为R)。

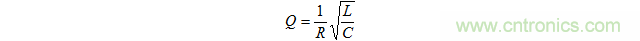

当如图11(a)所示在串联谐振中串联使用一个阻尼电阻器时,谐振器的Q可如下推导出来 :

(公式2)

例如,我们可以把图3-2-4的测试中使用的部件常量代入公式中。如果电阻器R的信号源输出阻抗为50Ω,可以得出Q = 6.3,表示谐振很强烈。如果电阻器R升高,Q会变小,从而减弱谐振。因此,可以发现,增加一个超过50Ω的电阻器可以减弱谐振。

通常而言,为了抑制谐振,会慎重选择电阻器,使Q设定为1或以下。

(2) 串联谐振电路的非振荡条件

为消除来自脉冲波形(如数字信号)的正脉冲信号、负脉冲信号或振铃,使用满足以下公式的电阻器来实现LCR串联谐振电路的无振荡条件。

(公式3)

公式(2)使Q为0.5或以下。

(3) 并联谐振电路的阻尼

相反,当如图11(b)所示在并联谐振中并联使用一个阻尼电阻器时,谐振器的Q可如下推导出来:

(公式4)

在这种情况下,电阻越小,谐振越弱。

图11 电阻器阻尼作用的示例

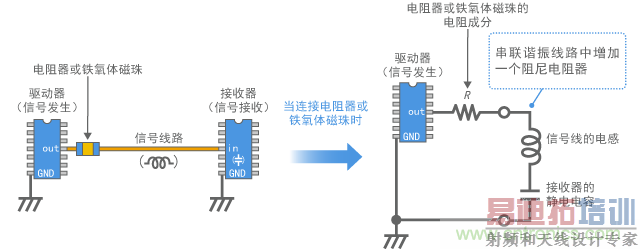

[p] 数字信号的阻尼(1) 阻尼电阻器和阻抗匹配电阻器

在利用阻尼电阻器防止如图9所示数字电路线路导致的谐振时,通常如图12所示将其与线路串联使用。在此期间,电阻越大,谐振抑制效 果越好。但是,如果阻尼过大,会产生副作用,如信号衰减和脉冲波形缓慢上升。因此,应根据噪声抑制与电路运作之间的平衡选择合适的电阻器。如果线路可以视 作传输线,可利用下一章节中讲述的阻抗匹配方法,以更为简便的方式完成这个操作。

(2) 铁氧体磁珠的阻尼作用

如图7和图8中的示例,铁氧体磁珠通常用于EMC对策中的阻尼。此时,应选择这个元件,使铁氧体磁珠的电阻(R)成分在谐振频率处满足公式(2)。由于铁氧体磁珠的阻抗具有频率特征,谐振可以得到抑制,同时还会最小化对信号波形的影响。此外,相比电阻器而言,铁氧体磁珠可吸收更大的直流电流。

图12 数字信号阻尼

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...