- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

减少峰值EMI解决方案

录入:edatop.com 点击:

中心议题:

在系统中,EMI不仅在各类时钟线路中发生减弱,还在所有与时钟同步的信号中减弱。而且,使用此技术的好处也随着系统中地址和数据总线数量的增加而不断增加。

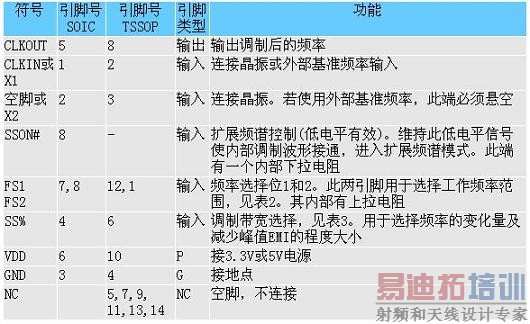

管脚排列与管脚功能

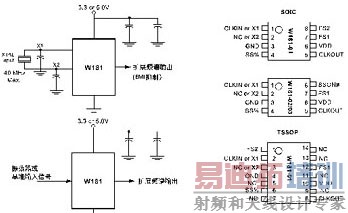

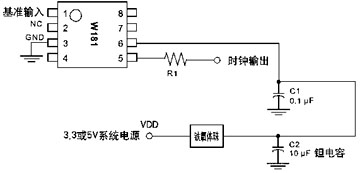

W181-01/02/03有8引脚SOIC封装及14引脚TSSOP封装,及其典型应用电路框图和三种封装管脚排列如图1所示。

功能描述

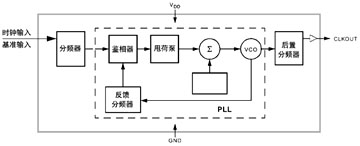

W181采用了频率锁相环(PLL)技术来调制输入时钟,其结果是得到一个输出时钟,它的频率可缓慢地扫过一个接近于输入信号的窄带。基本电路结构如图2所示。

[p]

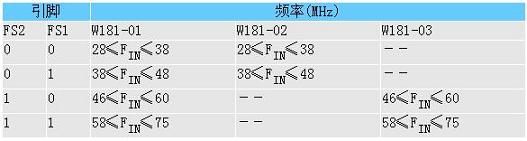

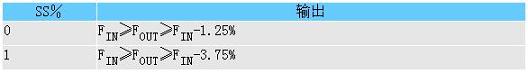

使用SSFTG进行频率选择

在扩展频谱时钟发生中,EMI减弱要依靠整形、调制率和调制波形的频率。当整形及调制波形的频率由已定的频率来确定时,调制的百分比就会有所不同。使用频率选择位(FS1及FS2)能设置频率范围。扩展率也被设到-1.25%之间。见表2。高扩展率加强了对EMI的减弱,然而,高扩展率却可能会因为超过系统最大额定频率或低于平均频率而使性能受到影响。鉴于上述原因,扩展率多在0.5%--2.5%之间。

扩展频谱定时信号的发生

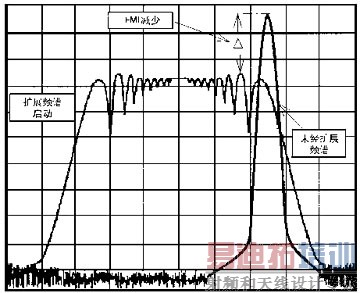

使用扩展频谱定时信号发生的好处如图3所示。它表示出了一个时钟谐波EMI的分布。将典型时钟的EMI与Cypress扩展频谱频率定时信号发生的EMI进行比较。请注意典型时钟中的尖峰信号,该尖峰信号使系统的准峰值EMI测试衰退。经过频谱扩展后,峰值能量将极大减少(至少8dB),因为能量通过一个更宽的带宽散发了。

调制波形

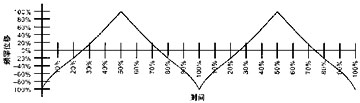

对EMI减弱的调制波形的整形是很关键的。调制的方案用来实现最大减小EMI,如图4所示。调制周期在X轴上以周期长度的百分比为单位。Y轴表示不同的频率值,也是以总扩展频率的百分比为单位。

应用指南

为了在系统应用中发挥最佳性能,应该用如图5所示的电源去耦方案。

- 减少时钟、数据总线峰值EMI解决方案

- 使用SSFTG进行频率选择

- 与扩展频谱定时信号对比分辨

- 对减弱的波形进行调制

在系统中,EMI不仅在各类时钟线路中发生减弱,还在所有与时钟同步的信号中减弱。而且,使用此技术的好处也随着系统中地址和数据总线数量的增加而不断增加。

管脚排列与管脚功能

W181-01/02/03有8引脚SOIC封装及14引脚TSSOP封装,及其典型应用电路框图和三种封装管脚排列如图1所示。

功能描述

W181采用了频率锁相环(PLL)技术来调制输入时钟,其结果是得到一个输出时钟,它的频率可缓慢地扫过一个接近于输入信号的窄带。基本电路结构如图2所示。

[p]

使用SSFTG进行频率选择

在扩展频谱时钟发生中,EMI减弱要依靠整形、调制率和调制波形的频率。当整形及调制波形的频率由已定的频率来确定时,调制的百分比就会有所不同。使用频率选择位(FS1及FS2)能设置频率范围。扩展率也被设到-1.25%之间。见表2。高扩展率加强了对EMI的减弱,然而,高扩展率却可能会因为超过系统最大额定频率或低于平均频率而使性能受到影响。鉴于上述原因,扩展率多在0.5%--2.5%之间。

扩展频谱定时信号的发生

使用扩展频谱定时信号发生的好处如图3所示。它表示出了一个时钟谐波EMI的分布。将典型时钟的EMI与Cypress扩展频谱频率定时信号发生的EMI进行比较。请注意典型时钟中的尖峰信号,该尖峰信号使系统的准峰值EMI测试衰退。经过频谱扩展后,峰值能量将极大减少(至少8dB),因为能量通过一个更宽的带宽散发了。

调制波形

对EMI减弱的调制波形的整形是很关键的。调制的方案用来实现最大减小EMI,如图4所示。调制周期在X轴上以周期长度的百分比为单位。Y轴表示不同的频率值,也是以总扩展频率的百分比为单位。

应用指南

为了在系统应用中发挥最佳性能,应该用如图5所示的电源去耦方案。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

上一篇:视频信号的干扰解决方法

下一篇:场效应管型号大全

场效应管型号大全pdf下载