- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

电源隔离和锁相环对于DSP中EMI的抑制

在高速的数字设计方案中,EMI是开发者必然需要面对的问题。以DSP为例,其非常容易受到电磁信号的干扰。因此开发者在进行设计时需要提前规划并发现噪声与干扰源,采取最佳的措施将干扰带来的损失降到最低。本文就将为大家介绍在DSP系统中如何有效避免噪声和EMI产生,对其中的电源隔离和锁相环进行介绍。

电源隔离和锁相环

如何实现最佳供电是控制噪声和辐射的最大挑战。动态负载开关环境很复杂,包括的因素有:进入和退出低功率模式;由总线竞用和电容器充电所引起的很大的瞬态电流;由于退耦和布线不合理引起较大的电压下降;振荡器使线性调节器输出过载。

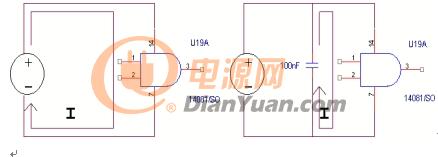

图1给出了一个设计电流回路的实例,其中利用了电源线退耦。该例中的退耦电容尽可能靠近DSP。如果没有退耦,动态电流回路将较大,这将加大电源电压的降幅,从而产生电磁辐射。

图1 电源退耦

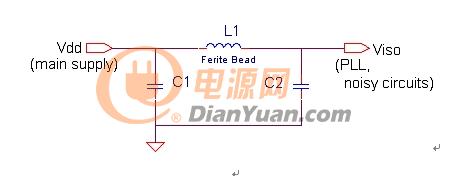

为PLL供电时,电源隔离是非常重要的,因为PLL对噪声非常敏感,并且对于稳定系统来说,要求抖动非常低。此外还需要选择模拟的还是数字的PLL,模拟PLL对噪声的敏感度比数字PLL要低。

图2 PLL电源隔离

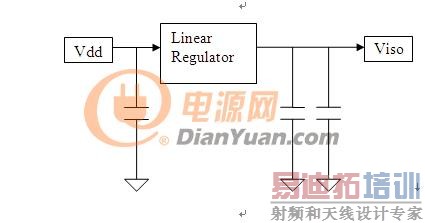

图3 利用LDO实现PLL电源的隔离

如图2所示的具有低截至频率的∏型滤波器经常被用来将PLL与系统中的其他高速电路隔离开。一个较好的办法是利用一个低压差(LDO)电压调整器来独立产生PLL的电源电压,如图3所示。该方法虽增加了成本,但确保了低噪声和优异的PLL性能。

通过以上的介绍,相信大家对于DSP系统中抑制EMI和噪声的方法有了一定的了解。电源隔离和锁相环是本文中给出的关键,本文中介绍的方法虽然会增加一定的成本,但却能够最大程度上规避EMI,希望大家在阅读过本文之后能够有所收获。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...