- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

去耦合对电磁兼容到底有什么影响

【导读】在考虑配电网(PDN)阻抗与同时开关噪声(SSN)和电磁兼容性(EMC)的关系时,了解去耦合的影响至关重要。如果一个PCB的功率完整性或去耦合特性较差,例如高PDN阻抗, 就会产生SSN和EMC问题。本文将通过实际案例,来证实PCB的PDN阻抗、SSN和EMC之间的关系。

本文通过实际案例,来证实PCB的PDN阻抗、SSN和EMC之间的关系。

在考虑配电网(PDN)阻抗与同时开关噪声(SSN)和电磁兼容性(EMC)的关系时,了解去耦合的影响至关重要。如果一个PCB的功率完整性或去耦合特性较差,例如高PDN阻抗, 就会产生SSN和EMC问题。本文将通过实际案例,来证实PCB的PDN阻抗、SSN和EMC之间的关系。

分析和结果

测试的原型为下面两个版本:一个由晶体振荡器提供外部50MHz参考的FPGA;三个主要接口:350MHz时钟速率的DDR2 SDRAM、150MHz的ADC数据总线和100MHz 的以太网。所有这些元器件都由1.8V降压转换器供电。通过表1中列出的测试案例,可以了解去耦合(包括PCB叠层和电容器)对SSN和EMC的影响。

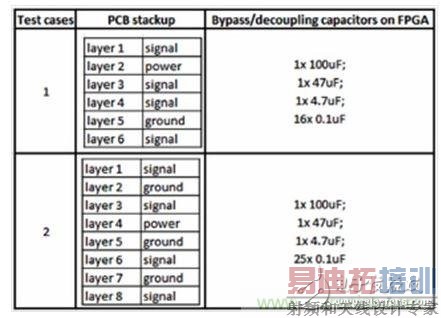

在测试案例1中,原型PCB包括四个信号层和一个接地层,有16个0.1μF去耦合电容器连接到PCB上FPGA的+1.8V电源引脚。在测试案例2中,原型PCB包括四个信号层和三个接地层,有25个0.1μF去耦合电容器连接到PCB 上FPGA的+1.8V电源引脚。

表1. 研究PCB去耦合对SSN和EMC影响的测试案例。

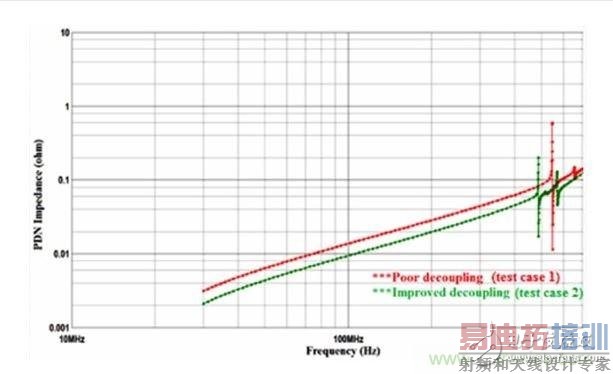

由图1的PDN阻抗曲线可以看出( 使用Mentor Graphic Hyperlynx软件对布局后期的功率完整性进行分析),相比测试案例1,测试案例2的电力网有更好的去耦合条件,因而在宽带范围内有更低的阻抗。0.1μF的电容器在中低频段(< 400MHz)会产生影响。另外,接地层的平面电容在频率高于400MHz时会产生影响。与测试案例1相比, 测试案例2有更多的去耦合电容器和接地层,因而具有更低的PDN阻抗。

图 1. PDN 阻抗图

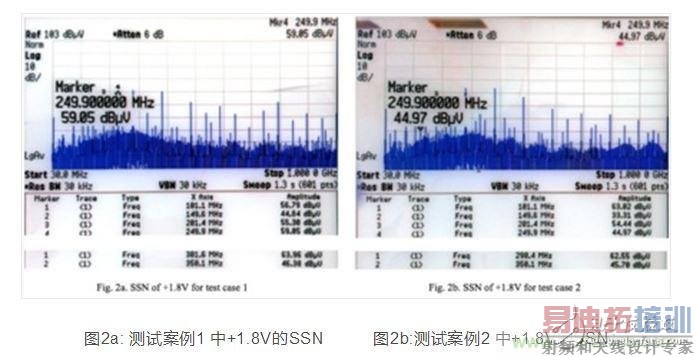

然后,对两个测试案例中频率跨越30MHz至1000MHz时+1.8V(使用频谱分析仪通过交流耦合探测)的功率频谱进行比较。参见图2b所示的测试案例2的频谱,所观察到的杂散主要是由晶体振荡器(50MHz基频)、DDR2 SDRAM (350MHz基频)、ADC数据总线(150MHz基频)和以太网(100MHz基频)的谐波造成的。在图2a所示的测试案例1中, 由于去耦合性能较差,频谱上出现了杂散,其功率达到最高。

PDN阻抗和晶体振荡器瞬态电流之间的相互作用, 加上在特定频率上同时开关或切换的IC输出缓冲器(即SSN),共同产生了电网噪声。通过改善去耦合降低功率阻抗,SSN和频率杂散便能得到抑制。

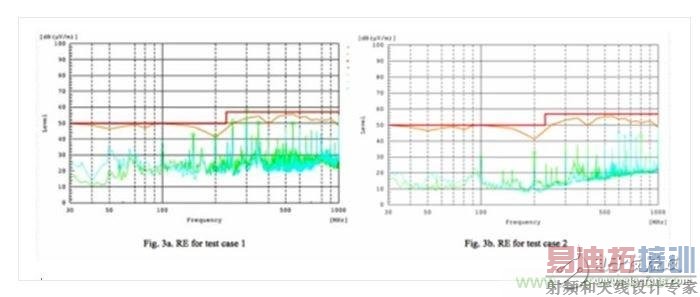

通过在3米的电波暗室进行辐射发射(RE)测试可以比较 两种测试案例的原型之间的噪声性能。测试案例2显示出比测试案例1更好的RE或EMC性能,测试案例2中有更多的接地层,这不仅能改善去耦合或PDN阻抗,还为沿PCB 迹线传输的所有信号提供了恰当的返回路径,从而进一步降低了辐射发射。

图3a: 测试案例1的RE 图3b:测试案例2的RE

结论

实际测试证实了去耦合对SSN和EMC的确会产生影响。因此,PDN和PCB叠层必须采用严格的方式执行, 以确保原型具有出色的质量、稳健性和功能。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...