- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一个关于DDR走线的问题

可以测一下DDR的时序让软件稍微调整应该能解决问题。你的线距是多少。

回楼上edqin,我的线距最小的位置是6mils,

别外一块板子也是同样的方案,我测了一下它的走线,基本上走了等长,

但不严格,最大的差入有200多mils,但是DDR离DSP很近,能正常工作,

难道是软件的问题?

CK/CK#和地址已经控制线要求等长,一般偏差在50~100mil,

LDQS/LDQS#,UDQS/UDQS#和数据线要求等长,一般偏差在50~100mil.

所有线的等长要求,不是很严格,但是一般不会超过100mil.

等长跟采样点有关,相关原理你看看DDR的手册。

不一定只是用软件来解决此问题代价要小一点。

是一开始录像就死机还是录了一会儿再死机?

回楼上的,是录了一会再死机.开机是很正常的.

哦这样的话,跟你的DDR走线没有多少关系.

当初HW是这样分析的:开机时DDR要交换的数据量不大,所以能正常,但是录像之后,因为是高清的,数据量比较大.所以就跑不起来了,想想也并非没有道理.当初我的地址线没有走等长,比数据线要长,是不是在读(写)数据时先要找地址,而我地址线太长而找不到地址(频率比较高)所以我的数据线走等长就没有意义了呢?

目前已经修改PCB了,等新PCB调试结果....

希望你改板后能有所改善. 建议此段时间你可以试试其它品牌的DDR.

不过我的愚见是:这个问题是你们的硬件有问题而不是板子有问题.

静待佳音!

频率高了对于走线长度是有限制的,走线较短的情况下等长就不是要求很严格了,如果走线较长尽量走等长,你的高8位等长,低8位等长的设置是有问题的,出现群体性差异,数据锁存是以时钟为准的。

过来学习 等待楼主的好消息

我也来学习一下!等待是否解决问题!

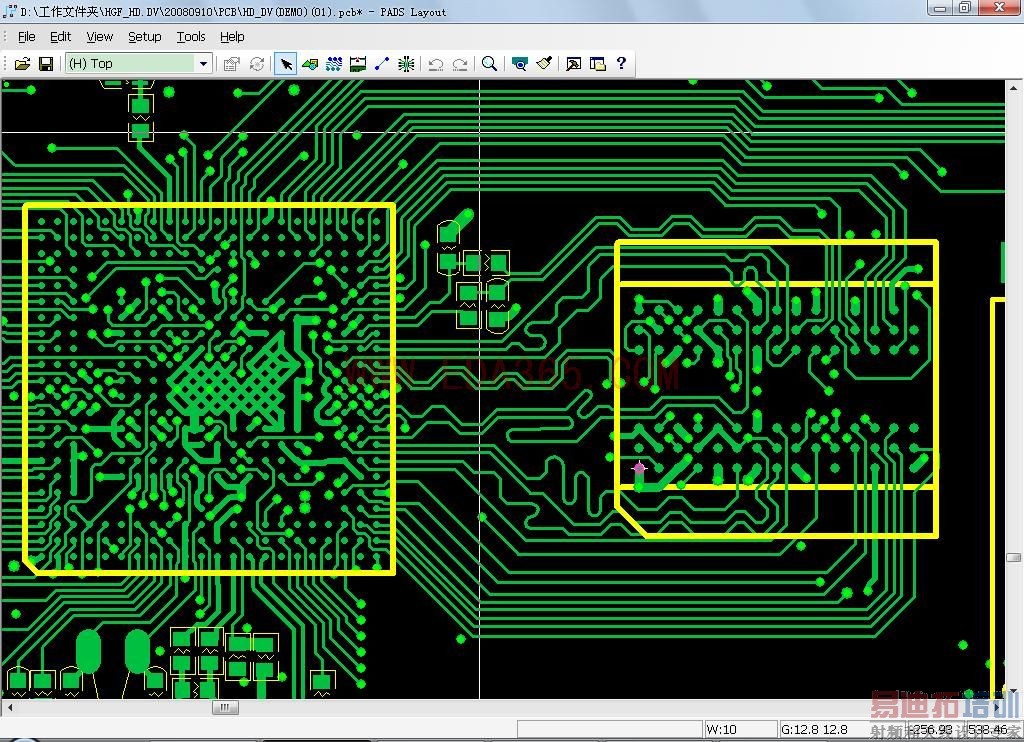

先上图

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

上一篇:浅谈电磁干扰对电感式接近开关的影响

下一篇:浅析变频器干扰及对策