- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

EMI板级设计

随着研发的项目越来越多,设计出来形形色色的电路板的各种各样的问题也会随着而来。有些莫名其妙的症状即便是“骨灰级”的工程师们也招架不住,更何况我们这等“菜鸟”级的热血青年。

EMI是板级设计不得不面对的,甚至也是最让人呲牙咧嘴的难点。很多时候即便我们小心小心再小心的设计出来的PCB也可能在随后的调试中由于哪怕只是一点点的疏忽而毁于一旦。特权同学也常常面对这样头疼的EMI问题,话说“吃一堑长一智”,真到关键时候还由不得我们,其实真正能提高工程师水平的还不是“遇一个问题解决一个问题”,应该要做到“遇一个问题解决一个问题再预防一打问题”那才叫境界。只可惜现实中达到这个高度也太不容易了,特权同学在面对EMI时还是一个接一个的败下阵来。半年前《遭遇空间电磁辐射》网络上都转得漫天飞舞了,这几天又是灰头土脸的哀怨糟糕的板级设计,正好再拿个反面典型以供“批斗”。

这是一个显示模块,作为缓存的SDRAM遭受了“重创”。图1的左图为无任何措施情况下的显示效果,看那个界面简直罗七八糟不堪入目。而右图在“重灾区”SDRAM和晶振的“天花板”上按了块铁皮,从此便“风平浪静”。

图1

[p]

究其根本原因,瞅瞅PCB布局布线便可知其一二。晶振是个大干扰源,敏感器件最好远离关键的数字信号,而此时的晶振却死皮赖脸的挨着其下的数条数据走线,尽管晶振的时钟输出做了包地处理,但是还是无法拦阻其造成的毁灭性破坏。

图2

原本以为故事已到此了解,但是远非这么简单,或者还可以深入探究根本原因。和缺氧弟沟通了这事,从他有过类似经历的同事那得到的建议是用示波器测测SDRAM的时钟信号的数据总线,看看他们是不是中央捕获,或者说算算他们的裕量到底有多少。对于这个建议特权同学很是嗤之以鼻,可不是,看到这个问题的时候首先想到的当然就是时序问题,因此无论如何精打细算的建立好时序模型,并且相应约束,甚至将10ns的相移范围基本都挨个段的尝试过,都无终而果。不过几个邮件下来看到缺牙老弟还是咬定必须做个测试,抱着试试看的心态也就拿着示波器下手了,探头一放到SDRAM端的clk管脚上,这一下可不要紧,界面完全正常了,和那块铁皮的效果如出一辙。啊,有过上次的经验,知道这个等效电容的探头起到了终端匹配的效果,于是立即动手顺势并上18pF的电容,如图3所示,问题果然迎刃而解。

[p]

图3

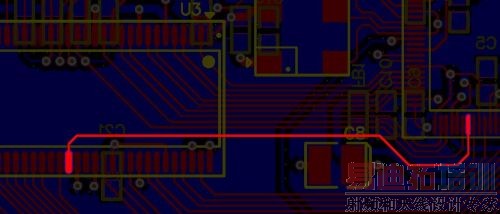

说到底,还是信号完整性问题,看看这条敏感线路的走线,如图4所示,以往很少会让它跑到芯片底部,而且离那个晶振还都有些距离,这回算是领教了。

图4

又是一个血的教训,撒money的经验,大家可要引以为戒,面对板级EMI,决不可掉以轻心。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

上一篇:严格的EMI要求

车载以太网将如何应对挑战

下一篇:影响EMC的因素和降噪技术