- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

平面磁集成EMI滤波器等效并联电容分析

【电源网】电磁干扰问题通常由于电路中表现不明显的耦合路径弄得很复杂,其明确而有效地解决方法一般都依赖于工程师的经验或建立在经典模型上的数模仿真。令工程师们高兴的是,如果所有的非接触电磁干扰都能够用传统的集总元件建模,而这种模型可以与转换电路图表相结合来描绘全部传导干扰和耦合干扰。这样分析和预测就变得比较容易了。

集总元件电路模型适合分析和预测频段在0~30 MHz的电磁干扰。在许多先前的研究和引出用于分析的所谓简单模型过程中,了解重要的路径通常至关重要。但是,在可能存在微小的耦合路径的情况下,这些参数都很难获得。为此,本文利用一种可用于分析所有容易产生非接触电磁干扰的普通集总电路模型,来准确地分析平面型PCB EMI集成滤波器。由于该模型更接近真实情况,因此更能如实反应平面型PCB EMI集成滤波器的滤波性能。

传统的分立元器件在低频状态下,往往作为理想器件(即当作纯电阻、纯电感、纯电容)来考虑。但在较高频率下,器件特性将远远偏离其理想特性,因此,就必须考虑高频分布参数对器件特性的影响。EMI电源滤波器中的主要元器件是电感和电容,为此,本文主要讨论电感和电容的高频分布参数对其滤波性能的影响。

因为EMI滤波器主要用于滤除高频噪声和高频干扰信号,而由于电容器电感器的等效寄生参数将严重影响电源滤波器的高频性能,因此,提高EMI电源滤波器的高频性能就应该重点提高EMI滤波器的高损耗,减小共模电感线圈的等效并联电容,同时减小电容器的等效串联电感。为了达到上述目的,本文提出了EMI电源滤波器的平面磁集成结构。

[p]1 EMI电源滤波器的平面磁集成结构

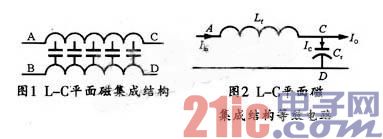

为了实现EMI电源滤波器的平面磁集成结构,这里引入了如图1所示的L-C平面磁集成结构。

图1中的这个结构是通过在平面绝缘板的两面直接嵌入两绕组导体而形成的,它通过控制绕组的连接点,使A、D为输入点,C、D为输出点。从而可等效得到如图2所示的低通滤波器。

1.1 集成CM(共模)滤波器的实现

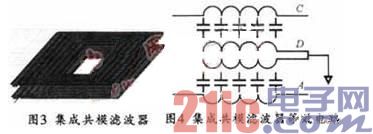

在共模励磁下,EMI滤波器可以等效为两个并联的低通滤波器。因此,集成CM滤波器可以通过如图3所示的两个集成L-C绕组线圈来实现,图3中的两个集成L-C绕组线圈都被连接成为低通滤波器形式,它们之间有很强的磁耦合,其对应的等效电路如图4所示。

1.2 集成DM(差模)滤波器的实现

差模滤波器的等效电路是一个崩型低通滤波器,其滤波电感值很小。大约在10~20 μH范围内,两个滤波电容值较大,其值在0.1~1 μF范围内。与分立EMI滤波器相同的是,在集成EMI滤波器中,差模电感也是利用集成CM扼流圈的漏感来实现的。在控制漏感值方面,平面CM扼流圈具有更多的灵活性,它可以在两个绕组线圈中间插入一层额外的磁性材料。因此不需要改变CM电感器的匝数,这样,漏感值就可以通过调整磁性材料的磁导率和有效面积来进行改变。这就给DM和CM电感器的解耦提供了一个机会。图5所示是集成滤波器差模电感模型,图6所示是集成滤波器差模电感的等效电路示意图。

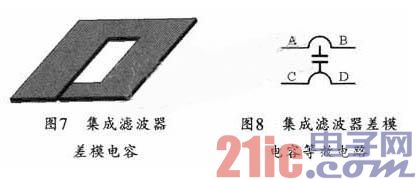

DM电容器可以用另一个连接成电容器的集成L-C绕组线圈来实现。它只有一匝或不到一匝,图7和图8所示分别是其差模电容及其等效电路。

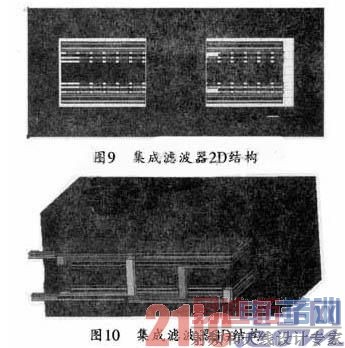

图9和10分别是平面型PCB EMI集成滤波器的二维结构和三维结构,该滤波器的所有参数都是通过该模型仿真得出的。

2 滤波器选材考虑

电源滤波器对高频EMI信号的抑制比低频EMI信号的消除容易得多,通常利用共模扼流圈的漏电感L所形成的差模电感就能消除0.3~30 MHz的传导干扰电平。设计和选用滤波电感器一定要根据电路的实际需要而定。一般0.01~0.1 MHz范围是差模干扰起主导作用.0.1~1 MHz范围内则是差模与共模干扰联合作用,而1~30 MHz范围主要是共模干扰起作用。因此,对滤波电感的磁性能要求完全不同。对共模电感要选用相对磁导率较高的材料,一般相对磁导率要达到15000左右;而差模则可选用相对磁导率低一点的,一般10~100左右。由于共模电容的地是接在机壳上,为了安全,共模电容不能太大,同时要选用介电常数高一点的,以增强电容的耐压能力。表1所列为不同物质的材料参数。

[p]3 等效并联电容的分析

由于这种L-C平面磁集成结构的两绕组靠得很近,因此,电网中的各种噪声往往会通过它们之间的分布电容耦合进电路。解决这一问题的最好办法是在初级和次级两绕组间增加一个如图11所示的静电屏蔽层,其中C1和C2分别为初次级绕组与静电屏蔽层之间的分布电容。

考虑到一个实际电感带有的等效并联寄生电容,其等效阻抗为:

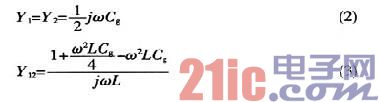

如果式(1)的分母中增加一项ω2L2C2(并且满足ω2L2C2=ω2L1C1),那么有Z=jωL1,这样就会变为理想的电感。基于这个想法,可以把一个电感器平分为两部分,并且将其中点连接电容接地。其模型及等效电路分别如图12和13所示。而将图13分别进行解耦和Y/△变换,其得到的等效电路分别如图14和15所示。且其变换参数为:

若令Gg=4Ce,Z12=1/Y12=jωL,这时电感将成为一个理想电感,绕组间的寄生耦合电容将减为零,可达到我们所期望的目标。附加电容Cg可以通过外加电容来实现,也可以利用绕组与地之间的寄生电容来实现。

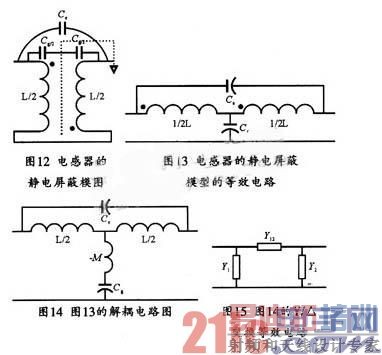

对于平面L-C磁集成结构,为得到期望的Gg,可在两绕组间加入地层,其平面结构如图16所示。设计时可采用:PlanaE43/10/28-3F和PLT43/28/4-3F3,绕组采用两层,每层3匝。绕组宽度为2mm,绝缘层厚度为0.07 mm。其等效电路如图17所示,若忽略绕组损耗和磁芯损耗,其中的L1、Cp1、Rp1t和Rs1分别为电感器第一半的电感和寄生参数;L2、Cp2、Rp2和Rs2分别为电感器另一半的参数;L3和Rs3为地层电感和电阻。忽略地层电阻时,其简化电路如图18所示。且有:

[p]

如果能满足Cg=4Ce,那么,线圈绕组间的寄生电容就可以减少至零。

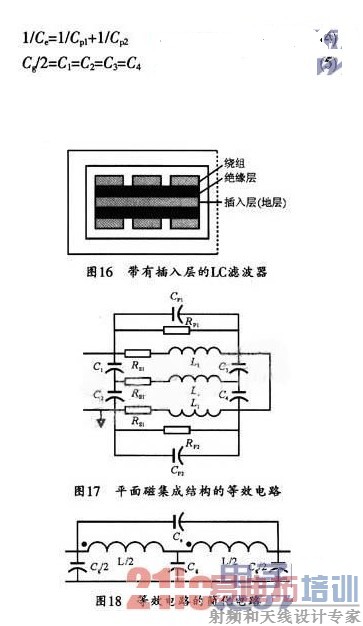

4 仿真验证

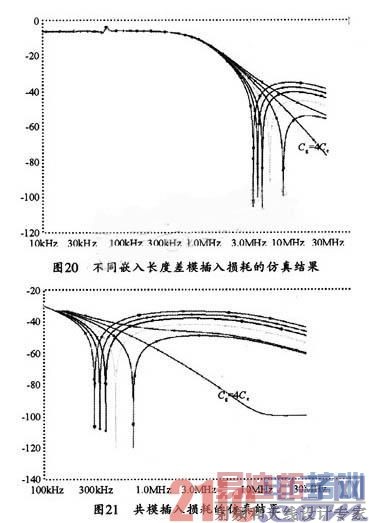

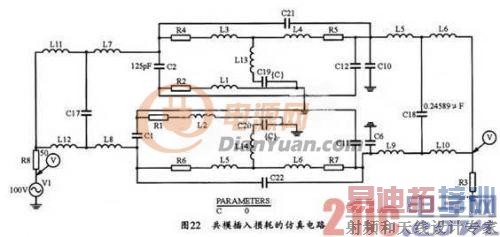

为了验证插入导电层是否能改善滤波器的高频性能,同时为了验证Ce与Cg的关系,可寻找理想的嵌入导电层长Xo之后以X为变量,得出的仿真结果如图19所示,然后再建立差模与共模仿真电路,并根据表1改变电容值Ce与Cg,所得出的差模插入损耗仿真结果如图20所示,而其共模插入损耗仿真结果如图21所示,图22为其共模插入损耗的仿真电路。

[p]

根据仿真结果可以看出,随着X不断增大,谐振点频率不断增大,在X=24.89 mm时,差模插入损耗表示出理想的状态。这时恰好Cg=4Ce。

5 结束语

仿真结果表明,嵌入导电层的滤波器可以去除EPC的影响,而且高频性能良好。滤波器的插入损耗在30 MHz以上都能达到-60 dB,并且有进一步减小的趋势。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

上一篇:手机电磁兼容测试分析及改善建议

下一篇:预防热电偶受干扰的有效措施汇总