- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何改良USB接口的EMI和ESD设计

时下流行的USB2.0接口具有高达480Mbps的传输速率,并与传输速率为12Mbps的全速USB1.1和传输速率为1.5Mbps的低速USB1.0完全兼容。这使得数字图像器、扫描仪、视频会议摄像机等消费类产品可以与计算机进行高速、高性能的数据传输。另外值得一提的是,USB2.0的加强版USB OTG可以实现没有主机时设备与设备之间的数据传输。例如。数码相机可以直接与打印机连接并打印照片,PDA可以与其它品牌的PDA进行数据传输或文件交换。

USB接口的传输速率很高,因此如何提高USB信号的传输质量、减小电磁干扰(EMI)和静电放电(ESD)成为USB设计的关键。本文以USB2.0为例,从电路设计和PCB设计两个方面对此进行分析。

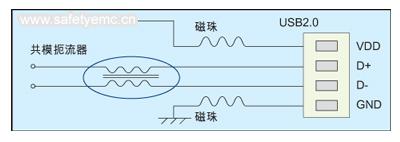

当USB2.0接口采用高速差动信号传输方式时,由于接地层与电源层的信号摇摆,放射噪声会有所增加。因此,为避免串扰并保证信号的完整性,消除将要混入高速信号中的共模噪声是电磁兼容设计的必要对策。在图1所示的电路中,数据电源线和地线上分别串联 一个阻抗为120欧姆、额定电流为2A的磁珠,而差分线对上则串联一个共模阻抗为90欧姆的共模扼流器。共模抗流器由两根导线同方向绕在磁芯材料上,当共模电流通过时,共模抗流器会因磁通量叠加而产生高阻抗;当差模电流通过时,共模抗流器因磁通量互相抵消而产生较小阻抗。

图1:USB2.0的噪声抑制电路图。

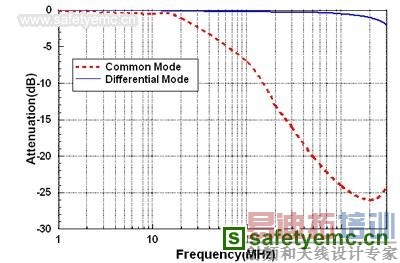

图2:SDCW2012-2-900的衰减频谱。

以深圳顺络电子有限公司生产的共模抗流器SDCW2012-2-900为例,该器件在100MHz的差模阻抗仅为4.6欧姆。从图2所示的衰减特性也能看出共模扼流器对差分信号不会造成影响,主要是针对共模电流进行选择性的衰减。

图3:USB2.0的ESD防护电路图

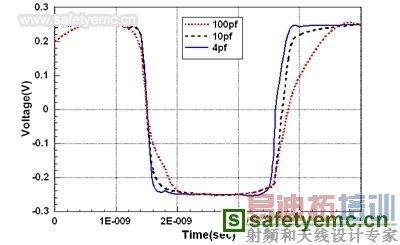

由于USB接口具有可热插拔性,USB接口很容易因不可避免的人为因素而导致静电损坏器件,比如死机、烧板等。因此使用USB接口的用户迫切要求加入防ESD的保护器件。在图3电路中,数据电源线、地线上各

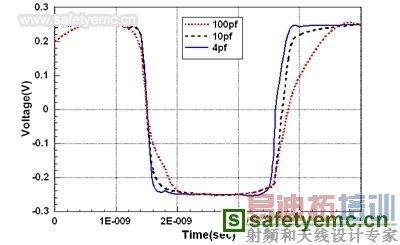

有一个工作电压为5.5V、电容为100pF的压敏电阻连到屏蔽地上。差分线对因数据传送速度高达480Mbps,则需要连接电容小于4pF的器件,因为较大的电容可导致数据信号波形恶化,甚至出现位错误。因此在差分线对上接入工作电压为18V、电容最大值为4pF的压敏电阻器。图4所示的电压波形也验证了电容为4pF的压敏电阻器(如深圳顺络电子有限公司生产的SDV1005H180C4R0GPT)对波形的影响不大。

图4:不同电容值的压敏电阻对波形的影响

对于USB2.0的PCB布线,需要考虑以下原则:

1.差分线对要保持线长匹配,否则会导致时序偏移、降低信号质量以及增加EMI;

2.差分线对之间的间距要保持小于10mm,并增大它们与其它信号走线的间距;

3.差分走线要求在同一板层上,因为不同层之间的阻抗、过孔等差别会降低差模传输的效果而引入共模噪声;

4.差分信号线之间的耦合会影响信号线的外在阻抗,必须采用终端电阻实现对差分传输线的最佳匹配;

5.尽量减少过孔等会引起线路不连续的因素;

6.避免导致阻值不连续性的90度走线,可用圆弧或45度折线来代替;

7.压敏电阻器的接地端要接入屏蔽地层,并放置在端口位置。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...