- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCB阻抗受控的通孔之设计

要想保持印制电路板信号完整性,就应该采用能使印制线阻抗得到精确匹配的层间互连(通孔)这样一种独特方法。

随着数据通信速度提高到3Gbps以上,信号完整性对于数据传输的顺利进行至关重要。电路板设计人员试图消除高速信号路径上的每一个阻抗失配,因为这些阻抗失配会产生信号抖动并降低数据眼的张开程度——从而不仅缩短数据传输的最大距离,而且还将诸如SONET(同步光网络)或XAUI(10Gb附属单元接口)等通用抖动规范的余量降到最低程度。

由于印刷电路板上的信号密度的提高,就需要更多的信号传输层,而且通过层间互连(通孔)实现传输也是不可避免的。过去,通孔代表一种产生信号失真的重要来源,因为其阻抗通常大约为25~35Ω。这么大的阻抗不连续性会使数据眼图的张开程度降低3dB,并会依据数据速率大小而产生大量的抖动。结果,电路板设计人员要么尝试避免在高速线路上使用通孔,要么尝试采用新技术,例如镗孔或盲孔。这些方法虽然有用,但却会增加复杂度并大大提高电路板成本。

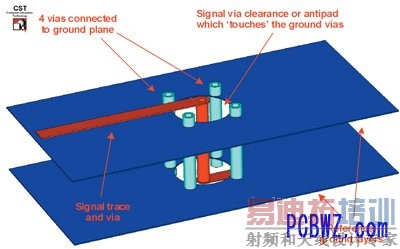

可以利用一种新的“类似同轴的”通孔结构来避免标准通孔出现的严重阻抗失配问题。这种结构以一种特殊的配置将接地通孔放置在信号通孔四周。采用这种技术设计的通孔在TDR(时域反射计)曲线上显示阻抗不连续性低于4%(50±2Ω)和信号质量有所改善。这种新方法产生一个阻抗可调的垂直通道。开发人员利用信号线在中心的简单同轴模型产生这种通孔结构;四周的接地屏蔽产生一个均匀分布的阻抗。四个在中心信号通孔四周排成一圈的接地通孔取代了均匀的接地屏蔽(图1)。因为这四个外通孔都连接到印制电路板接地或VDD(电源),所以它们携带电荷,而且其中每一个通孔与信号通孔之间形成电容。电容量的计算取决于通孔直径、介电常数以及信号通孔和接地通孔之间的距离。中心通孔的间隙(凹缘)“触及”外层通孔,所以电容量沿垂直通道均匀分布——防止每一电源平面和接地平面的电容量急剧增加。外侧的接地通孔为信号返回电流提供路径,并在信号通孔和接地通孔之间形成一个电感回路。

图1 印制电路板层间互连设计的新技术提供可预测的路径阻抗和改进的信号完整性。

你可以利用简单的公式(参考文献1)计算出由一个接地通孔与信号通孔形成的电容量和电感量。计算时,你可以假定这两个通孔实质上是两根直径相同的导线。D为通孔的直径,a为信号通孔和接地通孔之间的中心距。一对通孔的电感L的计算公式为:![]()

一对通孔的电容C计算公式为:![]()

因为主要由5个通孔构成的垂直通道是均匀的,因此一对通孔的的阻抗Z的计算公式为:![]()

公式1计算了标准双线系统的电容量。改进的通孔结构增加了三个额外的接地通孔,所以信号通孔中的正电荷量保持不变,但所有的负电荷则均匀地分布在四个接地通孔上。因此,改进的通孔结构的总电容量大约与双线系统的总电容相同。但是,这种通孔模型的电感量则是双线系统电感量的四分之一,因为信号通孔与四个接地通孔之间构成了四个并联的电感回路,从而通孔的阻抗Z为:![]()

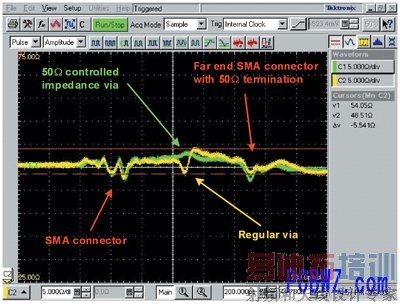

试验人员在从60密耳厚的6层电路板到130密耳厚的16层电路板上使用FR4 polyclad 370、Getec和Rogers电路板材料,对这种通孔结构进行了测试。他们利用TDR测量和基于CST(计算机仿真技术)的3-D场测定仪验证了计算所得的通孔阻抗。他们推导的公式预示无论电路板的厚度如何,阻抗都格外地好(±2Ω),因为通孔的阻抗公式与电路板厚度无关。表1将计算获得的6层62密耳FR4测试电路板(er=4.1)的阻抗与TDR测量结果和基于CST的Microwave Studio 3-D场测定仪仿真所得的阻抗值进行了比较。计算所得的通孔阻抗与测量结果的误差在±2Ω之内。

图2 黄色波形表示具有常规通孔的通道的TDR曲线。绿色波形表示具有阻抗受控通孔的通道的TDR曲线。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:CMOS集成电路的性能及特点

下一篇:高速PCB设计EMI规则探讨