- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCB导线设计技术(中)

本文将接续介绍电源与功率电路基板,以及数字电路基板导线设计。

宽带与高频电路基板导线设计

a.输入阻抗1MHz,平滑性(flatness)50MHz的OP增幅器电路基板

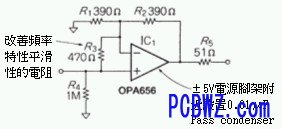

图26是由FET输入的高速OP增幅器OPA656构成的高输入阻抗OP增幅电路,它的gain取决于R1、R2,本电路图的电路定数为2倍。

此外为改善平滑性特别追加设置可以加大噪讯gain,抑制gain-频率特性高频领域时峰值的R3。

图26 高输入阻抗的宽带OP增幅电路

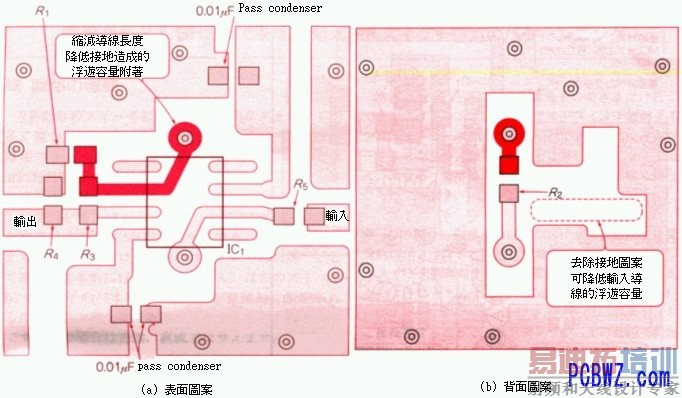

图27是高输入阻抗OP增幅器的电路基板图案。降低高速OP增幅器反相输入端子与接地之间的浮游容量非常重要,所以本电路的浮游容量设计目标低于0.5pF。

如果上述部位附着大浮游容量的话,会成为高频领域的频率特性产生峰值的原因,严重时频率甚至会因为feedback阻抗与浮游容量,造成feedback信号的位相延迟,最后导致频率特性产生波动现象。

此外高输入阻抗OP增幅器输入部位的浮游容量也逐渐成为问题,图27的电路基板图案的非反相输入端子部位无full ground设计,如果有外部噪讯干扰之虞时,接地可设计成网格状(mesh)。

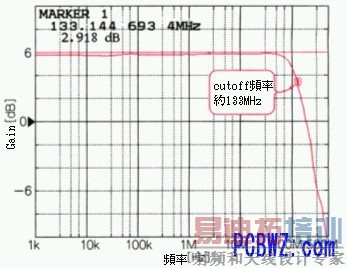

图28是根据图26制成的OP增幅器Gain-频率特性测试结果,由图可知即使接近50MHz频率特性非常平滑,-3dB cutoff频率大约是133MHz。

图27 高输出入阻抗OP增幅器的电路基板图案

图28 根据图26制成的OP增幅器Gain-频率

b. 可发挥50MH z~6GHz宽带增幅特性的电路基板图案

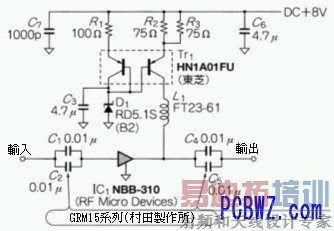

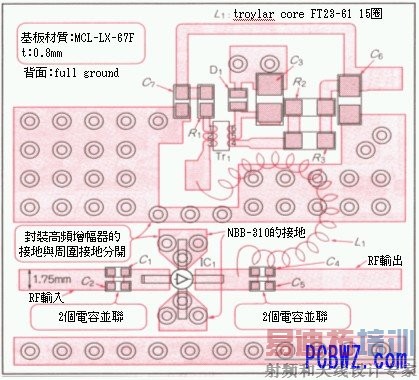

图29是由单芯片微波(MMIC: Monolithic Micro wave device)集成电路NBB-310(RFMicro Devices)构成的频宽50MHz~6GHz宽带高频增幅器,NBB-310高频组件采用AlGaAs HBT制程制作,因此可靠性相当高。

使用MMIC的增幅器时,必需搭配适合的电路基板图案阻抗与组件,例如耦合电容、高频扼流圈(choke)、线圈(coil)(以下简称为RFC)时,才能发挥组件具有的功能。如NBB-310技术数据的记载,偏压(bias)电流只需利用电阻与RFC即可,不过本电路使用复合型晶体管构成的current mirror电路,加上 NBB-310输出脚架的直流电压Level,会随着高频输入电力Level的变化,使用上述电阻与RFC简易偏压电路的话,输入电力变时输出脚架的直流电压会降低,NBB-310可能会有过电流流动之虞,所以偏压电路使用current mirror电路,藉此防止发生过电流现象。

图29 频宽50MHz~6GHz宽带高频增幅器的电路

频率超过2~3GHz必需谨慎选择印刷电路基板的材质,基本上不可使用传统FR4玻璃环氧树脂,因此无铅且高频特性与FR4玻璃环氧树脂相同的高Tg玻璃环氧树脂使用可能性大幅增加。一般而言高频电路通常会选用高频用低tan的基板材质,此外为抑制周围温湿度造成高频特性变动,因此必需将基板的温湿度一并列入考虑。图30是频宽50MHz~6GHz宽带高频增幅器的电路基板图案,如图所示micro strip line上方的2个耦合电容C1、C2与C4、C5, 并联设在线路端缘(edge)可以改善insertion loss与return loss等高频特性。

图30 频宽50MHz~6GHz宽带高频增幅器的电路基板图案

频率超过GHz等级时,电容器的高频特性随着厂牌出现极大差异,虽然指定厂牌对资材采购单位相当困扰,不过它是OP增幅性能上重要组件之一,重视应用性能时就不应该妥协让步。

封装NBB-310的接地面必需与周围接地面分离,如此才能够防止在NBB-310接地面流动的接地电流迷走在full ground面上,这种技巧经常被应用在改善OP增幅器的绝缘特性。

自制线圈时使用FT23-61 type的troy dull core,与直径ψ0.3polyurethane,靠近NBB-310端紧密绕卷5圈,接着均匀粗绕卷10圈;如果使用市售的线圈必需透过测试寻找特性符合要求的产品,笔者认为若使用WD0200A(冈谷电机)可以充分发挥NBB-310的性能。

c. 可以从直流切换成2.5GHz的RF切换电路

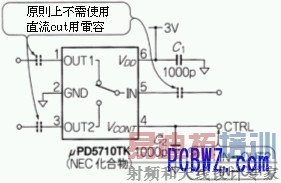

以往RF信号切换开关大多使用PIN二极管(diode),目前GaAs与CMOS专用IC已经成为市场主流,此处以μPD5710TK为例,介绍可以切换直流~2.5GHz的宽带切换电路(图31)。

图31 可从直流切换成2.5GHz的RF切换电路

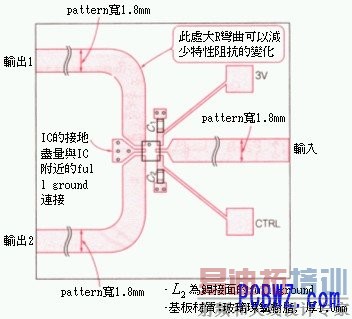

图中的μPD5710TK采用CMOS制程制作,点线表示直流cut用电容,其它切换IC的端子偏压(bias)Level是以直流性定义,所以几乎都是用电容直流cut,不过本电路无法使用直流电。图32是RF切换电路基板图案,图案宽度为1.8mm如此便可以成为Z0=50Ω的micro strip line的传输线路,电路基板厚度t=1.0mm。Layout基板时尽量让切换IC的的接地在附近流入背面的端子接地,如此切换控制线在端子附近强制性控制阻抗(impedance),所以没有长度与宽度等限制。

图32 可从直流切换成2.5GHz的RF切换电路基板图案

为避免切换控制端子影响IC的动作,因此作业上必需谨慎处理。图31的电容C1、C2与接地作交流性连接,可以降低电容对连接控制电路与电源图案的影响(图案成为等价性线圈,图案长度与频率关系的阻抗,从0到无限大巨大变动)。此外电容本身具备共振频率,所以本电路采用高自我共振频率与高定数电容,芯片电容一般都在100pF~1000pF左右。

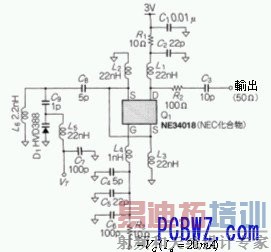

d. 4GHz VCO的电路基板图案

图33是4GHz为中心可作500MHz宽带振荡的VCO(Voltage Controlled Oscillator)电路,外观上看似可洱必兹基本电路,不过却无可洱必兹电路必要的C-C-L结构,然而本电路却显示负性阻抗而且还可以作振荡动作,一般的VCO为了要减轻负载,通常都会设置缓冲器(buffer),不过本电路50Ω负载时仍拥有良好的负性阻抗,所以直接连接至50Ω传输线路。

图33 4GHz为中心可作500MHz宽带振荡的VCO电路

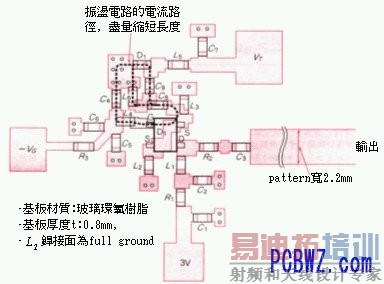

图34是电路基板图案。VCO的基板图案重点必需考虑决定振荡频率的组件,以及振荡晶体管的电流流动特性,依此才能设计最短的图案长度。如上所述电路50Ω负载时显示良好的负性阻抗,所以输出直接连接至Z0=50Ω的micro strip line的传输线路,此外控制电压端子Vr利用外部PLL电路以模拟电压控制,所以用C7作高频性降至ground,避免受到电路基板布线的影响。

图34 4GHz为中心可作500MHz宽带振荡的VCO电路基板图案

Q1、L6、L4、D1决定振荡频率,所以设计图案时必需考虑贯穿这些组件的电路电流路径。图34中的虚线表示电路电流路径。

接地采用via hole连接到L2,虽然这种连接方式属于full ground不过路径却非常短,此外via hole设计必需避免产生额外的阻抗。

4GHz的频率在真空中的1个波长为75mm,在印刷电路板上的波长比真空中更短,会有所谓的电路板上缩短率,加上电气上的长度只有该波长的1/2,几乎是可以忽略的长度,结果造成图案之间的距离变得非常短,所以必需尽量选用小型组件,设计电路基板图案时必需动作频率列为最优先考虑。

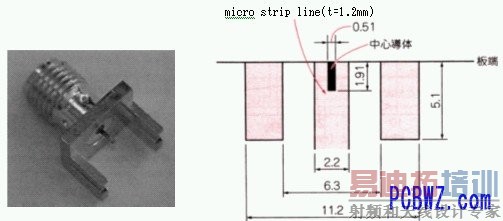

照片2是本电路使用的SAM连接器外观,它是Johnson components公司开发的End launch connector。对micro strip line而言,SAM的中心导体尺寸非常小,因此可以达成无阻抗暴增之虞的传输特性。图35是SAM连接器的电路基板图案,以及中心导体尺寸与基板厚度为1.2mm时的micro strip line宽度。

照片2 SAM连接器的外观 图35 照片2 SAM连接器的foot pattern

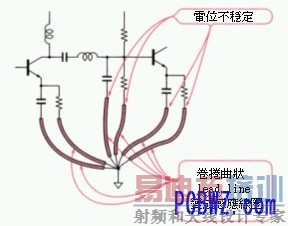

Audio电路大多采用单点接地(图36),类似RF电路的单点接地导线会成为电感器(inductance),使得各组件的接地端子之间电位变得非常不稳定,所以基板图案采用full ground设计,利用基板的背面与内层形成所谓的传输线路ground plain结构,此外与ground 连接的via hole会成为无法忽视的阻抗,设计上必需特别注意。

图36 Audio电路常见的单点接地

电源与功率电路基板导线设计

a.面封装型线性调整器的散热图案

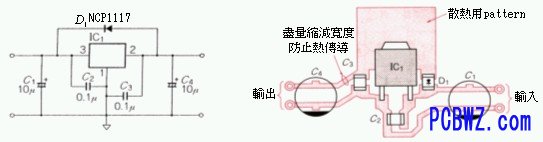

接着介绍输出电流1.0A低饱和型线性调整器(linear regulator)散热图案设计技巧。三端子调整器构成组件非常少因此广被使用,图37是由面封装型线性调整器NCP1117构成的降压电路;图38是降压电路基板图案。

图37 线性调节器构成的降压电路 图37 线性调节器构成的降压电路

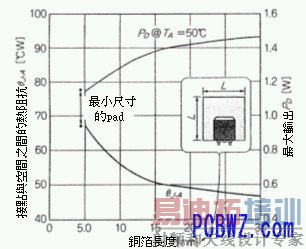

旁通电容器(bypass condenser) C1、C3封装在半导体的输出入端子附近,NCP1117为面封装型半导体,使用电路基板图案作散热。图39是NCP1117的散热pattern大小与容许电力-热阻抗的关系,例如输入8V,输出5V,输出电流400mA时,半导体的损失利用输出、入的电压差(8V-5V=3V),乘上输出电流后等于3V×0.4A=1.2W,根据图39可知NCP1117需要7mm正方以上的散热pad。直接与散热pad连接时,如果输出平滑电解电容C4的电路基板图案太宽时,热量会经由图案传导至电容器造成电解电容温度上升,所以散热pad与C4的基板图案必需案配合输出电流,尽量降低导线图案的宽度。

图39 NCP1117的散热pattern大小与容许电力-热阻抗的关系

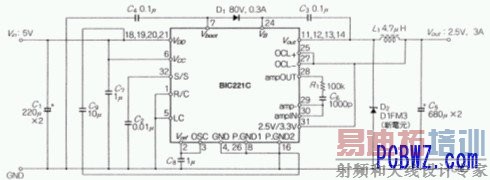

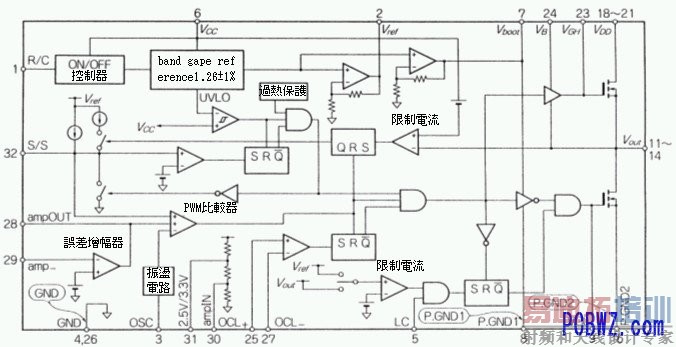

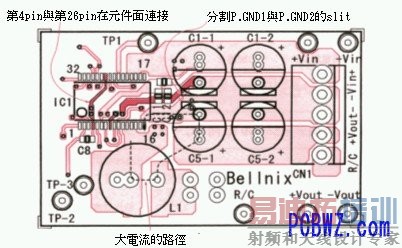

同步整流step down converter BIC221C与控制电路,以及MOSFET驱动电路三者同时封装成一体,本电路的动作频率为300kHz,输入5V,输出2.5V/3A。图40(a)是step down converter电路图;图40(b)是BIC221C的内部方块图;图41(a)是电路基板组件面图案。

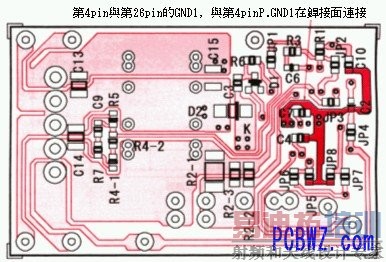

如图40(b)所示,BIC221C内部方块图所示第4,6号脚架的GND,与第8号脚架的P.GND1、第16号脚架的P.GND2明确分隔,如果按照图40(a)电路图指示,直接描绘含盖上述脚架配线图案的话,可能会造成误动作与噪讯增加等后果,因此设计电路基板图案时,必需将第8号脚架的P.GND1、第16号脚架的P,GND2分开,避免第4,6号脚架GND大电流流动。具体方法如图41所示,GND的第4,6号脚架在组件面连接,P.GND1的第8号脚架再与焊接面连接,大电流从C5通过P.GND2的第16号脚架,再从Vout(11,12,13,14pin)通过L1流入C5,P.GND1的第8号脚架从C1设置slit作连接,因此连接与第4,6号脚架的GND的图案不会有大电流流动。

(a)电路图

(b)BIC221C的内部方块图

图40 同步整流式step down converter BIC221C构成的step down converter

(a)组件面

(b)焊接图

图41 2.5V/3.3A输出的DC-DC converter电路基板图案

b. 光学耦合器构成的gate驱动电路基板图案

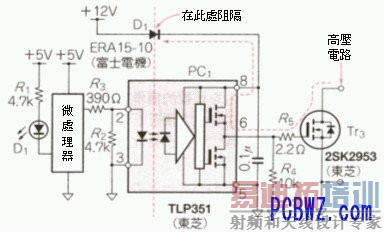

为避免控制电路遭受破坏,因此图42将光学耦合器TLP351与二极管构成的控制电路,以及功率MOSFET分离。

图42 photo coupler构成的gate驱动电路

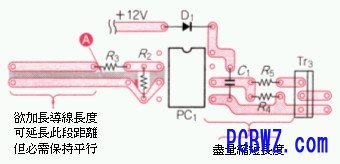

图43 gate驱动电路的基板图案,光学耦合器的光学二极管单元属于电流驱动,光学晶体管与功率MOSFET等gate驱动单元则是电压驱动,所以光学耦合器封装在功率MOSFET附近,此时必需避免光学二极管的正、负极的平行导线Ⓐ部位面积变大。

图43 gate驱动电路的基板图案

c. 专用IC构成的gate驱动电路基板图案

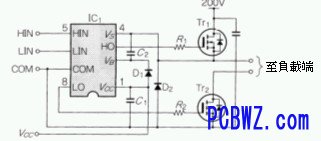

IR2011 8pin驱动IC内嵌high side与low side的gate驱动电路,属于D级audio增幅器与DC-DC converter的gate驱动器。

图44是专用IC的构成的gate驱动器电路;图45是驱动电路的基板图案。

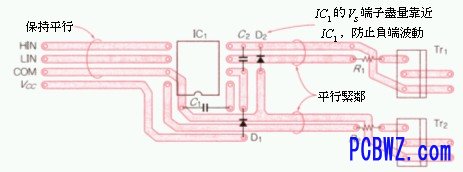

虽然设计上要求gate驱动IC尽量靠近功率MOSFET设置,远离功率MOSFET设置的场合,为避免high side的source电位波动,造成IC1第4脚架V5的负电位波动,所以需将二极管D2设在gate驱动IC附近。

此外为防止Tr1、Tr2误动作,因此source与gate的导线尽量邻接,此外控制信号的输入图案与COM图案两者必需平行设置。

图44 专用IC的构成的gate驱动电路

图45 专用IC的构成的gate驱动电路的基板图案

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电路板布线设计(二)模拟与数字布线技术差异之探索

下一篇:时域分析和频域分析