- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基础电路设计(七) EMC对策与雷击防护

前言

由于IC与LSI高速化与高度积体化,使得IC与LSI本身就成是巨大的噪讯发生源,此外基于低耗电量的要求,即使IC与LSI低耗电化或是低噪讯化,从机器整体的角度观之,机器对外部的噪讯反而变得极端敏感,因此有必要开发可抑制EMC等电磁干扰的技术。

噪讯对策可分为两种方式,一种是直接抑制噪讯,另一种方式是避免外部噪讯造成电磁性结合引发电路误动作,前者必需采取EMI对策,后者则需采取EMS对策。在电磁噪讯充斥的环境下设计电子电路,除了成本trade off考虑之外,概括性的对策手段摸索与理论的结合成为重要的手法,因此接着要深入探讨EMI与EMS的防护与对策。

IC与LSI高速化与封装时的噪讯对策

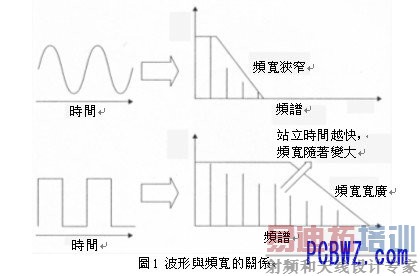

设计电子电路时选用适合电路动作速度的逻辑IC非常重要,如果IC动作速度超过设计上的要求时,系统与机器的带宽会大幅增加(图1),抑制机器产生的噪讯变得毫无意义,而且更不易进行EMC对策。最近大部分的电子机器都使用高速低电压CMOS IC,若与以往常用的TTL IC比较,CMOS IC反而更容易因噪讯造成电子电路误动作。噪讯发生源通常是在电流变化(di/dt)很大的部位。CMOS IC是在switching产生大电流(过渡电流与充放电电流)变化时动作,此时若流入具有有限阻抗(impedance)的ground line(主要是ind uctance成份),该部位就会发生电压下降现象,而压降造所成电路误动作,会因低电压IC的阀值越低越危险。相较之下高速IC的场合,即使是数ns的噪讯也会引发电路误动作,因此不论是设计电子电路或是封装设计,噪讯对策时必需注意以下要点:

(a).电源与接地层低阻抗化

双面电路基板对动作速度较低的数字电路,具有良好的低阻抗效应,因此接地可以采用如图2所示的网状(mesh)导线,如果能缩小电源‧接地(ground)所形成的回路面积(loop area),即使受到外部磁界影响产生诱导电流,由于该电流会相互抵销,因此整体而言双面电路较不易受到外部磁界影响。不过短、粗是设计电源‧接地导线的基本重要观念。复数导体时电源‧接地的导线,则需避免岛状分布。高速高性能电路通常是采用多层电路板,同时会将电源‧接地作为better面,信号传输线路尤其是阻抗(impedance)为80Ω左右时,最好使用micro strip line结构设计,如此便可降低传输线路的阻抗值,进而可让送信端能使用具有高驱动能力的IC组件。除此之外为了使电路能充分发挥应有特性与整合性,因此高速高频电路大多使用多层电路板。

(b).Switching噪讯

有关高速数字电路中CMOS IC的时间延迟问题,由于Bus是在某种tinning下同步进行switching,未作switching时虽然祇有数μA的漏电(leak),不过当switch ing动作时CMOS IC电路的电流中含有贯穿电流与充放电电流成份,由于贯穿电流与充放电电流会影响其它组件与电路,因此它是造成电路障碍的原因之一。

【计算实例1】

有关贯穿电流的影响,假设CMOS IC为32位Bus都是从0开始变化成1,每个位的贯穿电流为10mA,电源供给的电流ID :

ID=32x10mA=320mA

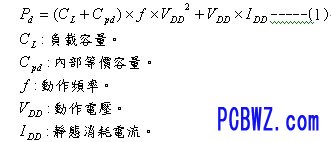

瞬间发生如此大的电流变化(di/dt),虽然导线的长度很短,不过LSI内部宽度祇有1μm以下微细导线的电压会急遽下降,造成LSI内部产生无法忽视的ground bounce现象。上述计算实例祇考虑贯穿电流的影响,事实上LSI内部流有充放电电流,该充放电电流随着动作频率不断变化,动作频率越高消耗电流越大。CMOS IC的消耗电流Pd 可由下式求得:

静态消耗电流IDD=Pd/VDD。最近IC不朝朝向低电压低耗电量方向发展,假设电源电压从5V变成3.3V低电压时,耗电量减少程度可利用式(1)求得:

VDD2=(3.3V/5)2=0.44=44%

亦即电源电压从5V变成3.3V低电压时,耗电量会降低44%。必需注意的是低电压化对IC/LSI的站立/下降时间几乎毫无影响,电压变化(dv/dt)与高频噪讯有直接关连,也就是说IC/LSI的低电压化,可以有效减少IC/LSI本身的噪讯。

【计算实例2】

8位shift resistor 74HC164的规格如下:

如上所述电源.接地pattern导线层内流有贯穿电流、负载充放电电流、终端阻抗驱动电流所构成的高频电源电流,而且电源.接地pattern导线层内还具有有限阻抗(impedance),如果switching动作电流流入电源.接地pattern导线层内时,就会因电压下降造成电路发生误动作。此外若用接口cable与外部机器设备连接时,接口cable会成为common放射的天线,造成其它机器受到干扰,换言之电源接地层内的高频电源电流是common放射的发射源,因此common放射成为EMI对策的重要对象之一。实施switching动作电流对策时的重点,分别是IC/ LSI的站立时间与下降时间。站立时间越快电源电流的带宽越大,放射至外部的电磁波带宽也越大,相对的就越不容易进行对策。对机器设备或是系统而言,维持最小带宽与抑制放射噪讯,成为最有效的EMI对策,换言之延迟IC/LSI的站立时间具有下列效果:

※抑制放射噪讯的发生。

※可以抑制负载容量充放电时的电流。

※可以减少反射的影响。

因此IC/LSI必需选择适合该电路特性的低速组件,因为避免使用超过电路特性的高速IC,可以减少不必要的噪讯以及电路误动作等困扰,这也是最有效EMI对策的基本概念。

接着要介绍decoupling在抑制电源.接地pattern导线层内高频电源电流时所扮演的角色。

(c).Decoupling Condenser

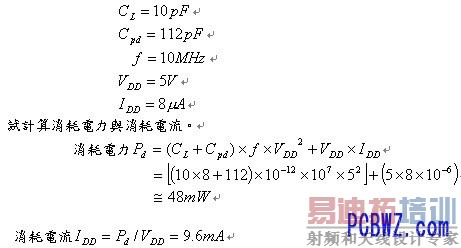

Decoupling Condenser原本的目的是利用电容器储存电荷,提供IC/LSI动作时必要的驱动电流,因此Decoupling Condenser必需具备可支持高速动作时贯穿电流等瞬间大电流的特性。传统的Decoupling Condenser祇需针对每个IC,使用0.01~0.1μF高频特性的陶瓷电容器即可,尤其是消耗电流与驱动电流之间无极大差异时使用TTL IC,基本上就不会造成特别的问题。不过IC高速化会使用信号站立时间变快,此外使用静止电流与驱动电流的比很大的CMOS IC时,Decoupling Con denser的封装方式则扮演关键性角色,由于Decoupling Condenser对电子电路具有重大影响,因此最近受到高度重视。图3是电容器(Condenser)的高频波等价电路,类似这样的电路并非单纯的Condenser,因为根本上lead端会存有寄生电感(Inductance),而寄生电感会使Condenser无法充分对应须状脉冲电流模样的贯穿电流、充放电电流,最后造成电路动作延迟等严重后果,此时Decoupling Cond enser却无法有效提供IC/LSI必要的驱动电流。造成上述现象主要原因是因为swi tch动作无法支持的电流,变成由电源提电流供,使得电源.接地pattern导线层内流有须状脉冲电流(高频电源电流)。

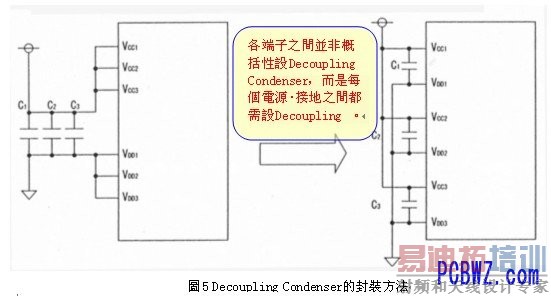

换言之为了使Decoupling Condenser可作高速动作,因此需设法使电感成份降至最低水平,常用手法是选择chip ceramic condenser作对策,该组件通常是设于电源.接地端之间导线长度最短的区域,藉此降低电感成份。在IC/LSI众多组件种类之中,有些组件有考虑电源.接地端的layout与Decoupling Condenser组装问题,有些组件则未考虑上述问题。多层电路板的电源.接地是由batter面构成,因此电源.接地即使是高频性,仍可见到阻抗(impendence)成份。IC/LSI用Decoupling Condenser的电荷属于低阻抗,所以祇要补正IC/LSI不足的驱动电流,高频电流就可以通过电源层流动。具体对策如图4所示,在电路上装设高频用inductor,如此一来就可提高高频阻抗(impendence),进而防止switching时的动作电流流出电源侧。如上所述当switching时,高频贯穿电流会在CMOS LSI内部电源与接地之间流动,为了抑制IC/LSI的高频大电流集中在电源.接地之间流动,同时减轻单位pin的电流,因此将电源与接地端子作多脚化(multi pin)设计成为常用的手段。如图5所示实际pattern封装设计时,并非概括性的设置Decoupling Condenser,而是在每个电源.接地之间设置Decoupling Condenser。

(d).信号线的终端

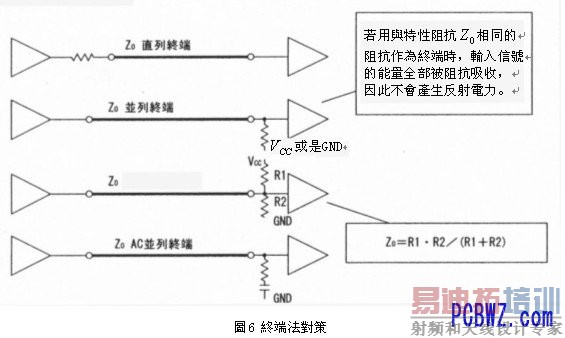

要让数字号产生的高频波带宽降至最低范围,基本上必需防止传输线路不整合所造成的over shoot与linking波形变动,因为如此一来除了可以防止电路误动作之外,还可使放射噪讯带宽变窄。图6是常用的对策方式,这种对策也称为终端法,不过最有效的终端法是并列终端法与Tabnan终端法。

(e)降低电流loop面积

某点的电磁波电界强度 可用下式求得:

E=K(f2AI/r) ------------------------(2)

K:定数。

f:频率。

A:电流loop的面积。

I:电流loop的电流大小。

r:至电流loop的距离。

由式(2)可知降低电界强度的条件是抑制 ,增加 值,也就是说要降低放射能量必需增加loop电流值,减少loop面积与频率同时加大物理距离。loop面积最小化意味着可以降低从该处放射的噪讯能量,同时还可以避免成为噪讯放射至外部的天线,使得电子机器不会产生或是接受噪讯,进而获得EMC防护对策的预期效果。除此之外layout封装线路时,必需注意平行邻接且长度较长的pattern,很容易发生cross talk使得噪讯值无法降低,因此必需特别谨慎处理。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...