- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种多频段电子电路及其设计方法

技术描述:

无线通讯产业已演进至多种标准/多种服务之境地,例如无线局域网络(Wireless Local Area Network, WLAN)使用2.4 GHz, 5.2 GHz, 5.7 GHz频段、GSM行动电话使用0.9 GHz, 1.8 GHz,1.9 GHz频段、而全球定位系统(Global Position System, GPS)使用1.5 GHz频段。因此最好能将多种标准整合在同一收发机芯片中,亦即要能设计制作出多频段收发机。 设计多频段收发机最主要的挑战,在于增进通讯收发机的功能之同时,能使用最少额外之电路。

习知设计多频段收发机中的低噪声放大器之策略是,针对某一频段就设计符合该频段的低噪声放大器。换言之,要设计能使用0.9 GHz, 1.8 GHz,1.9 GHz频段之三频收发机,就须设计三组低噪声放大器以因应三种不同频率。因此在设计低噪声放大器时,与其相关的增益、噪声指数(Noise Figure)、输入阻抗及输出阻抗,都是对某一特定频段来做设计。如此一来,多频段收发机之整个电路的面积及功率消耗,都要比单频段收发机大许多。本发明之目的在提供一种多频段放大器及其设计方法,仅使用单一放大器即可达成多种频段之输入阻抗匹配,而且不增加电感使用数量,也不需额外打线。

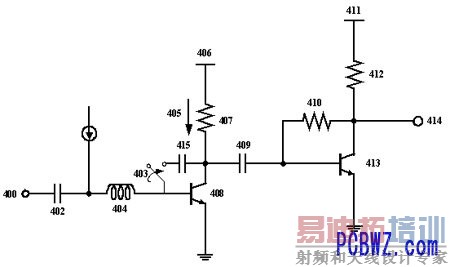

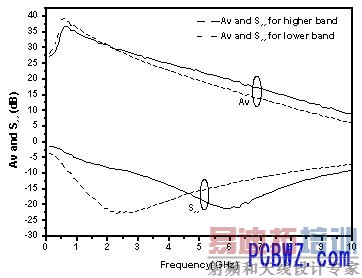

参阅图一,其乃本创作具2.4/ 5.2/ 5.7 GHz多频段处理功能之实施例的电路图。在此电路中我们虽使用双极晶体管,但使用场效晶体管也可以。第一电阻407与第二电阻412均为300奥姆;第三电阻410为600奥姆;直流阻隔/交流耦合电容409为3pF;该第一晶体管408与第二晶体管413射极面积均为12.18平方微米。制程采TSMC 0.35um SiGe BiCMOS制程。在此多频段低噪声放大器中,我们将一串联组合之一切换开关403及一电容器415电性连接于放大器中第一级晶体管408基极端与集极端之间。藉由此切换开关之导通与否,来改变看入第一级晶体管基极端之总输入电容CIN。CIN 和接在基极上的电感404,构成了达成输入阻抗匹配的共振腔。当切换开关403不导通,即切换开关403为断路时,此时在本实施例中接在基极上的电感404与看入第一级晶体管基极端之总输入电容CIN 组成之共振腔可达成在5.2/ 5.7 GHz(WLAN无线局域网络IEEE 802.11a)的输入阻抗匹配。当切换开关403导通,即切换开关403接近短路时,第一级晶体管基极端与集极端之间因多并联了一个电容器415,故看入第一级晶体管基极端之总输入电容CIN 增大,从而接在基极上的电感404与看入第一级晶体管基极端之总输入电容CIN 组成之共振腔可达成在2.4 GHz(WLAN无线局域网络IEEE 802.11b)的输入阻抗匹配。在输出端414部份,我们使用了回授电阻 410达成输出阻抗匹配。在不需输出阻抗匹配的情况下(例如zero-IF或low-IF接收机情况下),可不用回授电阻 410达成输出阻抗匹配。电阻407及电阻412为分别为第一级晶体管及第二级晶体管之负载。本实施例虽用电阻为负载,视需要使用电感或电容负载亦是可以的。重点是输入端能达成多频段阻抗匹配。由于我们只使用了一个电感404,而且是制作在芯片上的电感,因此不但整个电路可以完全在单一芯片上实现,而且电路的面积非常小。这对于商品化非常有利。图二是这个电路的量测结果,可以看出其输入阻抗的匹配程度(S11)在使用频段内,均小于-16dB以下,而增益则都有20dB以上。(1262字)

关键图式:

图一 多频带低噪声放大器电路图

图二 散射参书和电压增益量测结果

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:对高速电路设计的几点考虑

下一篇:恒定磁场基础要点