- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速电路设计中利用CTAB的阻抗补偿方法

本文介绍了RDRAM内存应用设计中利用CTAB进行阻抗补偿的技术,透过理论分析,探讨了其在高速电路设计中的推广应用价值。作者结合具体的设计实现,详细提出了工程应用运算公式及设置方法,以及CTAB‘电气延迟’效应的补偿方法。

本文讨论的CTAB源于参考文献[1]、[2]中的两个不同定义:‘Copper TAB’和‘Compensation TAB’。前者是从实体形态的角度定义,后者是从电气功效的角度定义,并且都缩写为CTAB。实质上,把两者结合起来能更全面地理解CTAB,即CTAB是一种在电路板上直接覆铜而形成的电容器,具有补偿讯号走线的阻抗非连续性的作用。

在上面的参考文献中,CTAB的应用都与RDRAM内存的设计相关,最初的目的都是用于补偿内存插座寄生的电感,匹配高速讯号的阻抗,修正讯号的完整性。

阻抗匹配问题的产生

由于芯片的制程不同,相对于SDRAM和DDR-SDRAM,RDRAM的工作频率要高很多。一般SDRAM的工作频率点为1336MHz和166MHz,DDR-SDRAM的工作参考频率点为1336MHz、1666MHz和200MHz,RDRAM的工作参考频率在400MHz或者533MHz。而且,这三种内存的讯号电平也有区别,SDRAM的电平为LVTTL,DDR-SDRAM的电平是SSTL,而采用的是RAMBUS定义的RSL讯号。RSL仅为800mV讯号摆幅,采用电流模驱动方式,要求讯号走线的阻抗严格控制在28Ω至40Ω之间。

根据上面的对比,在工作频率和讯号上,RDRAM的技术要求都相对较高。在实际应用中,要求在下面两个方面必须保证:一是各讯号走线的长度必须严格匹配,一般要求走线偏差控制在±10mil之内;二是讯号走线的阻抗控制在指定值的一定偏差范围之内,比如26Ω~30Ω。第一个要求可以透过控制走线的长度来实现,而讯号线的阻抗则很复杂,不容易解决。而且如果讯号的源端、末端阻抗不匹配导致阻抗特性不连续,必然会产生过冲、振铃讯号劣化现象,易造成讯号的误判,内存的储存存取将很容易出错,也必然会导致相关的硬件系统出错,最终影响系统的稳定性。

为解决这个问题导入了CTAB,透过在RAMBUS连接器的上增加容性负载来平衡连接器的电感,达到阻抗匹配的目的。

CTAB阻抗补偿的理论分析

当RDRAM的工作参考频率为400MHz时,讯号的上升沿、下降沿时间为0.6ns左右,相当于模拟讯号的1.3GHz频率点;在工作参考频率为533MHz时,讯号的上升沿、下降沿时间为0.5ns左右,相当于模拟讯号的2GHz频率点。按照这种对应关系,讯号应该属于传输线的范围之内,而不能用低频讯号的分析方法来处理。

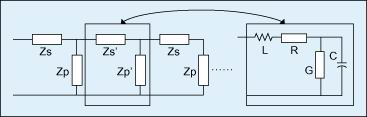

根据传输线的理论,RDRAM高频讯号部份的走线可以建构如图1所示的模型。在图左侧,根据传输线的理论将传输线表示为无数个微分线段的等效电路串联而成,其中Zs是串联阻抗,Zp是并联阻抗。在图1的右侧是每个微分线段的等效电路,其中L是单位长度的串联电感,R是单位长度的串联电阻,G是单位长度的并联电导,C是单位长度的并联电容器。且有如下关系成立:

![]()

在高频应用情况下,阻抗

![]()

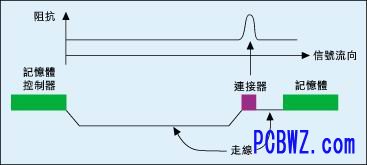

一般情况下,连接器的寄生电感值较大,而寄生的电容器值较小,所以特性阻抗大于印制板走线的特性阻抗,呈现图2中所示的阻抗分布。

根据公式(1),阻抗Z与讯号通路中的等效L和等效C有固定的关系,要使连接器的阻抗Z’等于目标阻抗Z0,从理论上分析,可以透过减少L’或者增大C’来实现。但连接器的等效电感L’、等效电容器C’是由连接器的实体形状和材质决定的,是一个既定值,无法改变。因此,在RAMBUS的设计中,是透过给连接器加上CTAB,增大等效电容器值实现阻抗补偿。

即:

![]()

经过补偿可以获得比较理想的阻抗特性。

CTAB扩展应用

CTAB虽然是在RDRAM设计中提出的一种阻抗调整方法,但是根据其原理可以扩大使用范围,广泛应用到高速电路设计中。

在硬件设计中,积木式模块化设计是一种趋势:一个产品可以按照功能划分为多个独立的功能子模块,约定好标准的接口,设计成多个硬件子模块,最后透过连接器组成一个系统。因此,讯号不可避免地经过连接器,根据前一小节的分析,必然会存在阻抗不连续而导致讯号劣化的问题。在电路设计中,讯号完整性是一个必须注意的问题。在高速电路设计中,在这方面尤其需要花更多的精力以保证讯号的完整性,使设计产品更加稳定可靠。

而另一方面,硬件设计中讯号的工作频率越来越高,从100MHz渐次发展到1GHz,甚至更高。在这些频率点的设计应当都视为高频设计,讯号线最好按照传输线的技术要求来慎重对待,尤其是在讯号线的走线长度超过了传输线的临界长度时(讯号从始端传输到末端,反射再返回到始端时间等于讯号上升时间,这种情况下的线长为临界长度)。 表1中给出了一些频率点对应的临界长度。

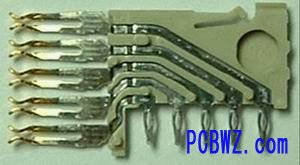

从表中给出的数据来看,在很多情况下讯号走线的长度超过了临界长度。比如高速背板设计产品,具有幅度小、频率高和讯号传输距离长的特点,且一般都至少两次经过连接器。在这些情况下,硬件设计中使用的连接器的阻抗特性必须加以补偿,否则整个走线中会存在两次阻抗跃变,最终由于阻抗不匹配而产生反射、振铃,劣化讯号质量。例如,在一般的背板设计中所使用的连接器大多数是标准的2mm连接器,其实物剖视图如图3所示。从图中可以看出连接器最长的引针比最短的引针要长很多,实际上在长度上最短的引针约长14mm,最长的引针约长23mm。如果连接器的特性阻抗与设计目标阻抗不一致,则最好在设计时加以补偿。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB的惨痛经历,值得工程师借鉴

下一篇:电容降压原理