- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

多途径降低FPGA设计的功耗

录入:edatop.com 点击:

每一代新的FPGA都变得速度更快、密度更高及规模更大。那么要怎么做才能确保功耗不同时增加呢?许多设计抉择,从明显的器件选择到更细微的状态机值选择等,都会对系统功耗构成影响。

为了更好地理解本文所要讨论的设计技巧如何能节省功耗,让我们先对功耗做一个简要介绍。

功耗包含两部分:动态功耗与静态功耗。动态功耗是指对器件中的容性负载进行充放电所需的功耗。它很大程度上取决于频率、电压和负载。这三个变量中的每一个都能由你以某种形式进行控制。

静态功耗是指由器件中所有晶体管的泄漏电流(源极到漏极以及栅极泄漏,常常集中为静止电流)所引起的功耗之和,以及任何其他恒定的功耗需求。泄漏电流在很大程度上取决于结温和晶体管尺寸。

恒定功耗需求包括因端接(如上拉电阻)所造成的电流泄漏。没有多少措施可以用来影响泄漏,但却能控制恒定功耗。

尽早考虑功耗

你制定的功耗决策在设计的早期阶段具有最大的影响。决定采用何种元件对功耗有很大的意义,而在时钟上插入一个 BUFGMUX 则影响甚微。因此须尽早考虑你下一个设计的功耗。

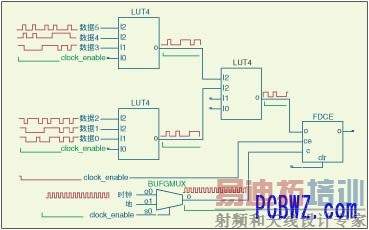

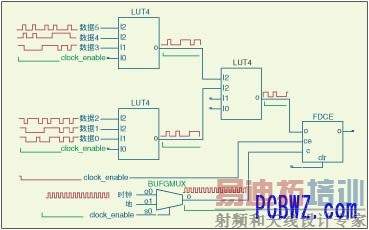

图1:利用使能信号来减少功耗。

并非所有元件都拥有同样的待机功耗。作为一种通用法则,器件工艺尺寸越小,晶体管的速度就越快,但漏电功耗也越高。不过,并非所有工艺技术都完全一样。例如,面向领域优化的90nm平台FPGA的待机功耗与其他90 nm FPGA技术的待机功耗有很大的差异。面向领域优化的90 nm平台FPGA采用一种称为三栅极氧化层 (triple-oxide) 技术的新工艺方法,通过有选择地增加栅极氧化层厚度来减少泄漏电流(同时又不牺牲性能),而有效地解决了静态功耗问题。尽管这个三栅极氧化层仍很薄,但这些晶体管的确展现出比标准薄氧化层晶体管更低的漏电流。据我们研究,90 nm平台FPGA的静态功耗比上一代130 nm平台FPGA的静态功耗要低一半。我们相信这是FPGA历史上第一次在迁移到新的、尺寸更小的工艺节点时静态功耗减小。

不过,虽然待机功耗随着工艺尺寸的减小而增加,动态功耗却将下降,因为更小的工艺尺寸往往伴随着更低的电压和更小的电容。因此请仔细考虑何种功耗对你的设计影响更大——是待机功耗还是动态功耗?

除了通用逻辑单元外,一些FPGA及CPLD器件还拥有专用逻辑,包括块RAM、18 x 18乘法器、DSP48块、SRL16以及其他逻辑。你应该总是采用专用逻辑,而不是基于逻辑单元的模块。专用逻辑不仅具有更高的性能,而且所要求的密度更低,因此对于同样的操作其功耗也更低。当评估你的器件选择时,请仔细考虑专用逻辑的类型与数量。

选择一项合适的I/O标准也能节省功耗。这些都是简单的决定,如选择最低驱动强度或较低电压标准等。当系统速度要求使用高功率I/O标准时,你可计划一个默认状态来降低功耗。有些I/O标准(例如GTL/+等)需要使用一个上拉电阻才能正常工作。因此,如果该I/O的默认状态为高而不是低,则可节省流过该端接电阻的直流功耗。对于GTL+,将50 ohm端接电阻的默认状态设置为1.5V,可使每个I/O节省30 mA的电流。

数据使能

当总线上的数据与寄存器相关时,常常使用片选或时钟使能逻辑来控制寄存器的使能。进一步讲,尽早对该逻辑进行“数据使能”,可以阻止数据总线与时钟使能寄存器组合逻辑之间不必要的转换,如图 1 所示。红色波形表示原设计;绿色波形表示修改后的设计。

另一种选择是在板上(而不是在芯片上)进行这种“数据使能”。例如,你可以用一个CPLD从处理器上卸载掉一些简单任务,使其能更长久地处于待机模式。同样的概念也可运用于FPGA。尽管FPGA不一定拥有待机模式,但用CPLD来截取总线数据并有选择地将数据馈送给FPGA,亦可节省不必要的输入转换。一些CPLD具有一种称为“数据门控”的特性,此特性可以禁止引脚上的逻辑转换到达 CPLD 的内部逻辑。数据门控使能可由片上逻辑或一个引脚来控制。

状态机设计

你应该根据预测的下一个状态条件来列举状态机,同时选择在通常状态之间具有较少转换位的状态值。这么做,你就能减少状态机网络的转换量(转换频率)。确定常态转换并选择适当的值,是一种可减少功耗同时对设计影响较小的简单方法。编码方式越简单,所使用的译码逻辑也就越少。

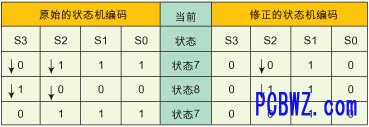

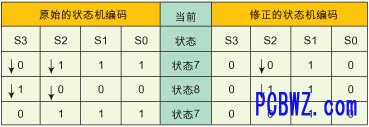

让我们来看一个在状态7和状态8之间频繁进行状态转换的状态机。如果你为该状态机选择二进制编码,则意味着每次在状态7和状态8之间转换时,都有四位需要改变状态,如表1所示。

表1:通过状态编码来减少信号转换。

如果状态机采用格雷码而不是二进制码来设计,则这两个状态之间的转换所需的逻辑转换量将降至仅为一位。另外,如果将状态7和8分别编码为0010和0011,亦可达到同样的效果。

时钟管理

在一个设计的所有吸取功耗的信号当中,时钟是罪魁祸首。尽管时钟可以运行在100 MHz上,但从该时钟派生出的信号却通常运行在主时钟频率的较小分量(通常为12% ~ 15%)上。此外,时钟的扇出也一般较高。这两个因素表明,要降低功耗,须认真研究时钟。

如果设计的某个部分可处于非活动状态,则可考虑使用一个BUFG-MUX(而不是使用时钟使能)来禁止时钟树翻转。时钟使能将阻止寄存器进行不必要的翻转,但时钟树仍然会翻转,从而消耗功率。不过,采用时钟使能总比什么措施也不用强。

你还应隔离时钟以使用最少量的信号区。不使用的时钟树信号区不会翻转,从而降低该时钟网络的负载。细心的底层规划可在不影响实际设计的情况下达到此目标。

功耗估算工具

Xilinx提供了两种形式的功耗估算工具:一种是称为“Web功耗工具”的实现前工具,另一种是称为“XPower”的实现后工具。Web功耗工具可基于对逻辑使用率的大致估计提供功耗估算。利用它,你可以仅凭设计利用率估计就能获得功耗评估,而无需实际设计文件。

XPower用于分析实际器件利用率,并结合实际的适配后 (post-fit) 仿真数据(VCD 文件格式),给出实际功耗数据。利用 Xpower,你可以在完全不接触芯片的情况下分析设计更改对总功耗的影响。

基于Web的功耗估计,是在设计流程的早期获得器件功耗情况的最快捷和最方便的方法。这些工具每季度都会发布新版本,因此信息总是最新,且不需要安装或下载,只需拥有互联网连接和一个 Web 浏览器即可。你可以指定设计参数并保存和加载设计设置,从而免去通过交互使用重新输入设计参数的麻烦。只要有对设计行为的估计并选定目标器件即可开始。

Xpower 是所有Xilinx ISE(设计工具配置中的一个免费组件,你可以用它来对设计的功耗需求进行更为详细的估计。XPower是在映射或布局与布线后设计的基础上对器件功耗进行估计的。对于成熟的量产FPGA及CPLD,XPower计算出的功耗估计的平均设计批量误差小于 10%。它将把器件数据与你的设计文件结合起来综合考虑,并根据你的特定设计信息来给出器件功耗估计的高精度报告。

XPower直接集成在ISE软件中,可提供分层及详细网络功耗显示、详细总结报告和功耗向导。XPower可接受仿真设计活动数据,并可以 GUI 模式和批处理模式运行。XPower 将考虑设计中的每个网络和逻辑元素。ISE 设计文件提供准确的资源使用情况、XPower 交叉参考布线信息以及特征化电容数据。设计特征化将对新器件持续进行,以给出最精确的结果。Xpower 采用网络翻转速率和输出负载,后再计算功耗和结温,并能显示单个网络的功耗数据。

为了更好地理解本文所要讨论的设计技巧如何能节省功耗,让我们先对功耗做一个简要介绍。

功耗包含两部分:动态功耗与静态功耗。动态功耗是指对器件中的容性负载进行充放电所需的功耗。它很大程度上取决于频率、电压和负载。这三个变量中的每一个都能由你以某种形式进行控制。

静态功耗是指由器件中所有晶体管的泄漏电流(源极到漏极以及栅极泄漏,常常集中为静止电流)所引起的功耗之和,以及任何其他恒定的功耗需求。泄漏电流在很大程度上取决于结温和晶体管尺寸。

恒定功耗需求包括因端接(如上拉电阻)所造成的电流泄漏。没有多少措施可以用来影响泄漏,但却能控制恒定功耗。

尽早考虑功耗

你制定的功耗决策在设计的早期阶段具有最大的影响。决定采用何种元件对功耗有很大的意义,而在时钟上插入一个 BUFGMUX 则影响甚微。因此须尽早考虑你下一个设计的功耗。

图1:利用使能信号来减少功耗。

并非所有元件都拥有同样的待机功耗。作为一种通用法则,器件工艺尺寸越小,晶体管的速度就越快,但漏电功耗也越高。不过,并非所有工艺技术都完全一样。例如,面向领域优化的90nm平台FPGA的待机功耗与其他90 nm FPGA技术的待机功耗有很大的差异。面向领域优化的90 nm平台FPGA采用一种称为三栅极氧化层 (triple-oxide) 技术的新工艺方法,通过有选择地增加栅极氧化层厚度来减少泄漏电流(同时又不牺牲性能),而有效地解决了静态功耗问题。尽管这个三栅极氧化层仍很薄,但这些晶体管的确展现出比标准薄氧化层晶体管更低的漏电流。据我们研究,90 nm平台FPGA的静态功耗比上一代130 nm平台FPGA的静态功耗要低一半。我们相信这是FPGA历史上第一次在迁移到新的、尺寸更小的工艺节点时静态功耗减小。

不过,虽然待机功耗随着工艺尺寸的减小而增加,动态功耗却将下降,因为更小的工艺尺寸往往伴随着更低的电压和更小的电容。因此请仔细考虑何种功耗对你的设计影响更大——是待机功耗还是动态功耗?

除了通用逻辑单元外,一些FPGA及CPLD器件还拥有专用逻辑,包括块RAM、18 x 18乘法器、DSP48块、SRL16以及其他逻辑。你应该总是采用专用逻辑,而不是基于逻辑单元的模块。专用逻辑不仅具有更高的性能,而且所要求的密度更低,因此对于同样的操作其功耗也更低。当评估你的器件选择时,请仔细考虑专用逻辑的类型与数量。

选择一项合适的I/O标准也能节省功耗。这些都是简单的决定,如选择最低驱动强度或较低电压标准等。当系统速度要求使用高功率I/O标准时,你可计划一个默认状态来降低功耗。有些I/O标准(例如GTL/+等)需要使用一个上拉电阻才能正常工作。因此,如果该I/O的默认状态为高而不是低,则可节省流过该端接电阻的直流功耗。对于GTL+,将50 ohm端接电阻的默认状态设置为1.5V,可使每个I/O节省30 mA的电流。

数据使能

当总线上的数据与寄存器相关时,常常使用片选或时钟使能逻辑来控制寄存器的使能。进一步讲,尽早对该逻辑进行“数据使能”,可以阻止数据总线与时钟使能寄存器组合逻辑之间不必要的转换,如图 1 所示。红色波形表示原设计;绿色波形表示修改后的设计。

另一种选择是在板上(而不是在芯片上)进行这种“数据使能”。例如,你可以用一个CPLD从处理器上卸载掉一些简单任务,使其能更长久地处于待机模式。同样的概念也可运用于FPGA。尽管FPGA不一定拥有待机模式,但用CPLD来截取总线数据并有选择地将数据馈送给FPGA,亦可节省不必要的输入转换。一些CPLD具有一种称为“数据门控”的特性,此特性可以禁止引脚上的逻辑转换到达 CPLD 的内部逻辑。数据门控使能可由片上逻辑或一个引脚来控制。

状态机设计

你应该根据预测的下一个状态条件来列举状态机,同时选择在通常状态之间具有较少转换位的状态值。这么做,你就能减少状态机网络的转换量(转换频率)。确定常态转换并选择适当的值,是一种可减少功耗同时对设计影响较小的简单方法。编码方式越简单,所使用的译码逻辑也就越少。

让我们来看一个在状态7和状态8之间频繁进行状态转换的状态机。如果你为该状态机选择二进制编码,则意味着每次在状态7和状态8之间转换时,都有四位需要改变状态,如表1所示。

表1:通过状态编码来减少信号转换。

如果状态机采用格雷码而不是二进制码来设计,则这两个状态之间的转换所需的逻辑转换量将降至仅为一位。另外,如果将状态7和8分别编码为0010和0011,亦可达到同样的效果。

时钟管理

在一个设计的所有吸取功耗的信号当中,时钟是罪魁祸首。尽管时钟可以运行在100 MHz上,但从该时钟派生出的信号却通常运行在主时钟频率的较小分量(通常为12% ~ 15%)上。此外,时钟的扇出也一般较高。这两个因素表明,要降低功耗,须认真研究时钟。

如果设计的某个部分可处于非活动状态,则可考虑使用一个BUFG-MUX(而不是使用时钟使能)来禁止时钟树翻转。时钟使能将阻止寄存器进行不必要的翻转,但时钟树仍然会翻转,从而消耗功率。不过,采用时钟使能总比什么措施也不用强。

你还应隔离时钟以使用最少量的信号区。不使用的时钟树信号区不会翻转,从而降低该时钟网络的负载。细心的底层规划可在不影响实际设计的情况下达到此目标。

功耗估算工具

Xilinx提供了两种形式的功耗估算工具:一种是称为“Web功耗工具”的实现前工具,另一种是称为“XPower”的实现后工具。Web功耗工具可基于对逻辑使用率的大致估计提供功耗估算。利用它,你可以仅凭设计利用率估计就能获得功耗评估,而无需实际设计文件。

XPower用于分析实际器件利用率,并结合实际的适配后 (post-fit) 仿真数据(VCD 文件格式),给出实际功耗数据。利用 Xpower,你可以在完全不接触芯片的情况下分析设计更改对总功耗的影响。

基于Web的功耗估计,是在设计流程的早期获得器件功耗情况的最快捷和最方便的方法。这些工具每季度都会发布新版本,因此信息总是最新,且不需要安装或下载,只需拥有互联网连接和一个 Web 浏览器即可。你可以指定设计参数并保存和加载设计设置,从而免去通过交互使用重新输入设计参数的麻烦。只要有对设计行为的估计并选定目标器件即可开始。

Xpower 是所有Xilinx ISE(设计工具配置中的一个免费组件,你可以用它来对设计的功耗需求进行更为详细的估计。XPower是在映射或布局与布线后设计的基础上对器件功耗进行估计的。对于成熟的量产FPGA及CPLD,XPower计算出的功耗估计的平均设计批量误差小于 10%。它将把器件数据与你的设计文件结合起来综合考虑,并根据你的特定设计信息来给出器件功耗估计的高精度报告。

XPower直接集成在ISE软件中,可提供分层及详细网络功耗显示、详细总结报告和功耗向导。XPower可接受仿真设计活动数据,并可以 GUI 模式和批处理模式运行。XPower 将考虑设计中的每个网络和逻辑元素。ISE 设计文件提供准确的资源使用情况、XPower 交叉参考布线信息以及特征化电容数据。设计特征化将对新器件持续进行,以给出最精确的结果。Xpower 采用网络翻转速率和输出负载,后再计算功耗和结温,并能显示单个网络的功耗数据。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:不同NRZ(No

Return

to

Zero,不归零)测试码型的适用场合

下一篇:利用TI

GHz

DSP性能可以实现哪些设计?

射频和天线工程师培训课程详情>>