- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

并行设计FPGA和PCB,应对系统设计的趋势与挑战

复杂度日益增加的系统设计要求高性能FPGA的设计与PCB设计并行进行。通过整合FPGA和PCB设计工具以及采用高密度互连(HDI)等先进的制造工艺,这种设计方法可以降低系统成本、优化系统性能并缩短设计周期。

图1:FPGA和PCB设计团队必须并行工作,不断地交换数据和信息以确保系统设计成功。

电子工业背后的推动力是对更快、更便宜的产品的需求以及在竞争厂商之前将产品推向市场。IC技术的进步一直以来就是促使功能增加和性能提高的主要因素之一,而FPGA技术也一直以非常快的速度在发展。与过去FPGA仅仅用作胶合逻辑不同的是,现在FPGA已经被用来实现主要系统功能。FPGA的逻辑门数已达1千万,内核速度达到400MHz,能提供高达11Gbps的下一代芯片间通信速度。而与此同时,它仍然保持着非常合理的成本,因此,与ASIC和定制IC相比,FPGA是一种更具有吸引力的选择。

IC和FPGA技术的进步对下游产业产生的效应影响到了PCB行业,这些高管脚数和高性能封装推动新的PCB生产及设计技术具有诸如嵌入无源器件、数千兆位信号和EMI分析等功能,并对专用的高密度和高性能布线提出了需求。基本的系统设计方法也在发生变化,对FPGA和PCB的设计可以并行进行以降低系统成本、优化系统性能并缩短设计周期。

PCB和FPGA一般是在不同的设计环境下创建,过去这些设计方案很少相互沟通。然而,随着高性能、高密度FPGA器件的日益流行,为满足紧张的上市时间表,如今PCB和FPGA设计团队必须并行工作(见图1),不断地交换数据和信息以确保整个系统设计获得成功。

当在PCB上实现高端FPGA时,设计工程师面临性能优化和系统设计生产率的双重挑战。设计工程师必须问自己:是什么问题使得过程慢了下来?需要做什么来获得最佳性能?这些问题的答案可帮助他们鉴别可实现更小、更便宜和更快系统的解决方案。

设计效率的挑战

设计工程师需要并行设计PCB和FPGA时,FPGA设计工程师再也不能像以前那样独立地设计,然后将完成的FPGA设计交给PCB设计工程师就可了事。一个有竞争力的设计要求FPGA和PCB设计工程师从上至下的协作,各自做些折衷以保证最后得到一个最优系统。并行设计的好处是它能减少设计周期、优化系统性能并降低制造成本。

图2:创建和更新FPGA的PCB原理图符号所需时间的估计。

并行设计的挑战在于FPGA布局和布线工具得到的结果需要准确、迅速地映射到原理图和PCB布局中,同时PCB设计的任何改变也必须在FPGA上更新。传统的设计过程是先设计FPGA,然后再将它们交给PCB设计工程师进行电路板实现,如今这种做法不再可行。

如果FPGA设计/综合、布局/布线以及PCB设计环境没有被整合,FPGA和PCB方案之间的沟通必须用人工的方法来实现。对于有几百个管脚的小型FPGA,这可能还可以接受,但是,如今很多设计拥有多个高度复杂的FPGA,使用这种方法进行信息沟通将非常浪费时间,并容易出错。仅仅是高管脚数FPGA的PCB原理图符号的创建和更新,就可以凸显这个问题(设计时间的评估见图2)。

另外一个问题涉及到PCB上的大型FPGA。与小型FPGA的符号不同,大型FPGA的单个符号在一张原理图放不下。这些符号必须通过功能分组被分成几个符号,并在FPGA的设计反复过程中保持不变。

FPGA设计工程师花费大量时间调整性能、选择正确的I/O管脚驱动器/接收器,然而FPGA的设计并非仅受FPGA设计工程师的控制。当在PCB上进行FPGA的布局和布线时,设计环境可能要求改变FPGA的管脚分配,如果PCB工具中没有FPGA设计规则,这可能成为一个重复而费时的过程。

此外,FPGA 的I/O分配也成了一个系统问题。设计工具需要能够管理管脚分配,但它们必须能被PCB和FPGA设计工程师用来沟通管脚约束。PCB设计工程师无法创建一个阻止FPGA时序收敛的条件,而FPGA设计工程师也不能创建一个阻止系统时序收敛的条件。

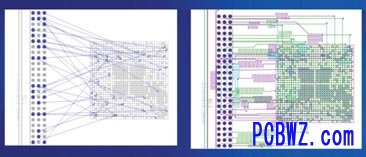

图3、图4给出的例子体现了装配在PCB上的FPGA的性能优化前后的布线情况。FPGA的32位总线必须直接与左边连接器进行通讯,这是一个高速总线,其上所有网络必须匹配以获得适当的偏斜控制。

在图3中,为使所有的走线长度与最长网络相匹配,布线器增加了很多蛇形走线。从PCB布线的角度来看,其结果是一团糟:有很多额外的拥塞、太多额外的走线以及一个工作性能并非最优的总线。

图3:FPGA性能优化前的布线图。

在图4中,布线器也对所有的走线长度与最长走线进行了匹配。即使这样,每条走线的长度也只有1.8英寸,而此前为3.2英寸,更短的匹配长度使总线延时减少到320皮秒。这种性能优化是整合FPGA和PCB设计过程的结果,它可获得理想的FPGA管脚图。

这个例子说明了在PCB上装配FPGA可能存在的挑战,包括:额外的拥塞需要更长的PCB设计时间完成布线;并非最优的系统性能;额外的布线要求额外的PCB层,从而增加制造成本。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:关于当前主流SI工具的特点

下一篇:(论坛问答)匹配电阻应放在什么位置?