- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

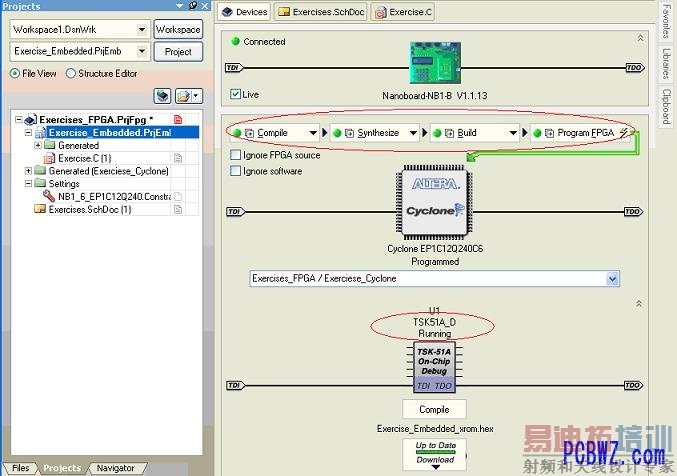

在Nexar上实现一个完整的嵌入式系统

以下我们将结合一个实例来简要介绍一下如何在Nexar上实现一个完整的嵌入式系统设计过程。

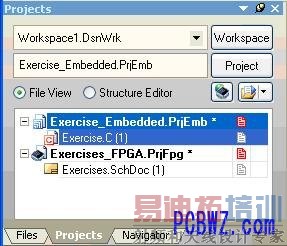

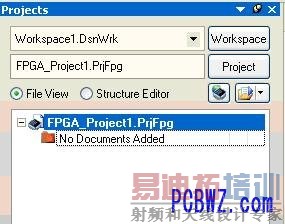

首先:创建一个新的FPGA工程

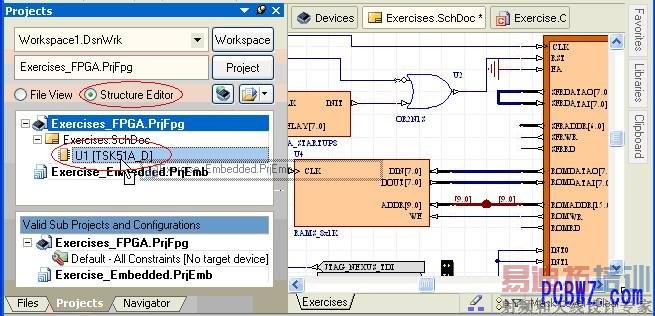

1、选择菜单 [menus]File>>New>>FPGA Project,在工程栏中将会显示新建的FPGA工程名,选择菜单[menus]File>>Save Project,在对话框中修改工程名称,然后Save。在工程栏中选择File View选项,在工程中将会列出所有属于当前工程的文件。注:Structure Editor选项用于编辑工程中文件间的链接关系。

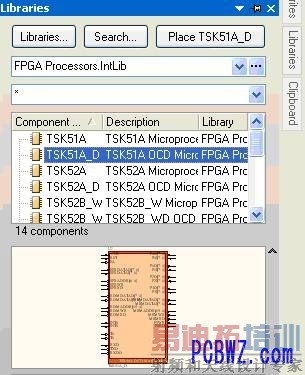

图1.1 工程栏----创建FPGA工程

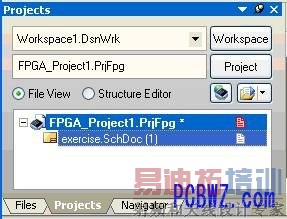

2、FPGA工程可以支持原理图和VHDL文件两种源文件,采用混合编辑时,可以将VHDL生成图表符的形式。选择菜单[menus]File>>New>>Schematic;也可以在工程栏中选中FPGA工程名,然后点击鼠标,选择[popups]Add New to Project>>Schematic。保存原理图,重新命名为exercise.schdoc。

图1.2 工程栏----创建原理图

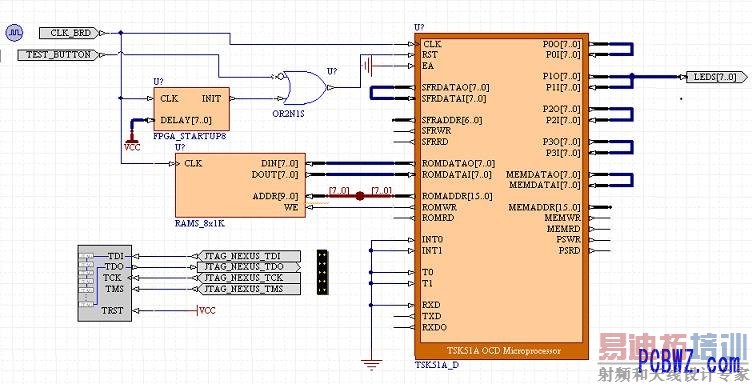

3、接下来在新加入的原理图中完成一个最简单的基于51内核的设计工程,实现LED闪亮的功能。在这个实例中,将会用到51的内核、RAM存储器、上电时序控制、异或门、Nexus协议接口等FPGA工程器件。Nexar2004的器件均可以在FPGA集成库中找到,在系统缺省设置下,在窗口右侧上方可以看到favorities/libraries/clipboard三个属性栏,单击libraries属性栏,窗口中弹出集成库窗口(见图1.3)。选定设计中需要的器件,并拖拽到原理图中。

| 器件名称 | FPGA集成库 |

| TSK51A_D | FPGA Processors.IntLib |

| RAMS_8x1K | FPGA Memories.IntLib |

| CLOCK_BOARD | FPGA NanoBoard Port-Plugin.IntLib |

| TEST_BUTTON | FPGA NanoBoard Port-Plugin.IntLib |

| LED | FPGA NanoBoard Port-Plugin.IntLib |

| NEXUS_JTAG_CONNECT | FPGA NanoBoard Port-Plugin.IntLib |

| NEXUS_JTAG_PORT | FPGA Generic.IntLib |

| OR2N1S | FPGA Generic.IntLib |

| FPGA_STARTUPx | FPGA Peripherals.IntLib

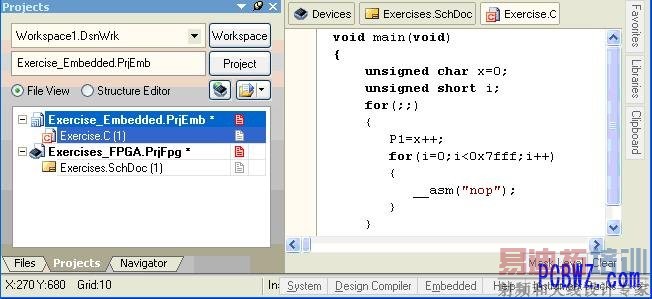

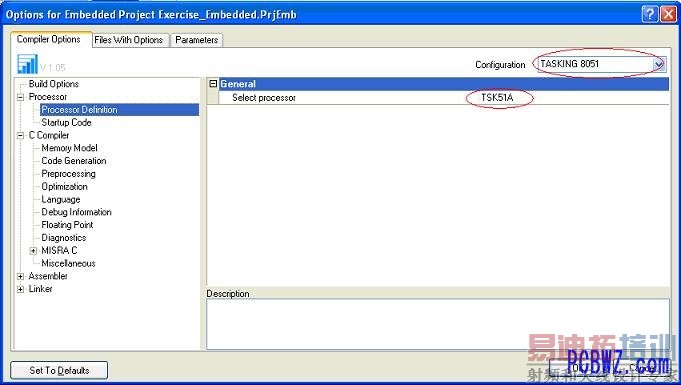

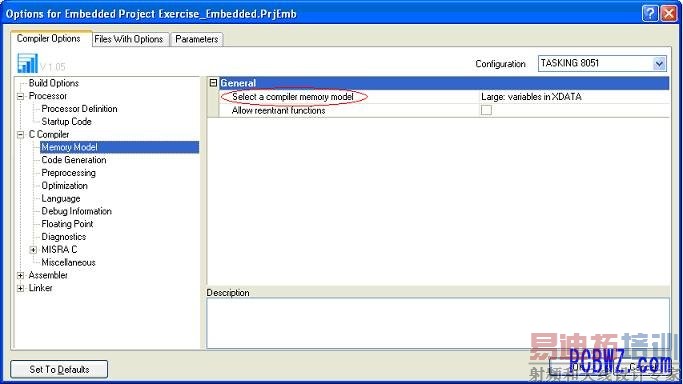

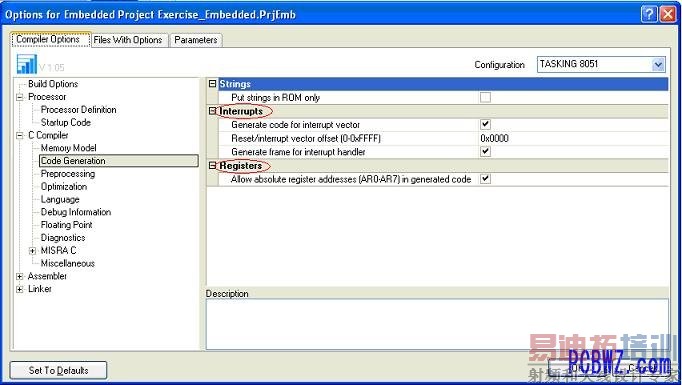

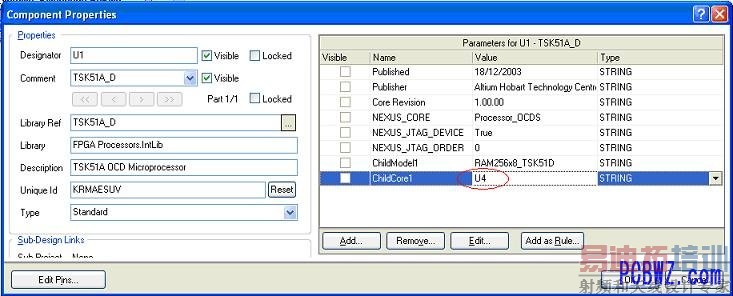

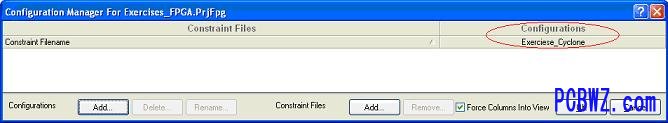

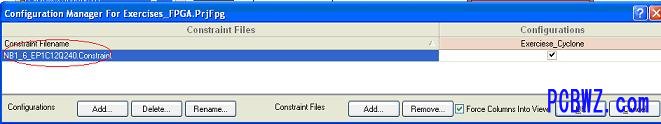

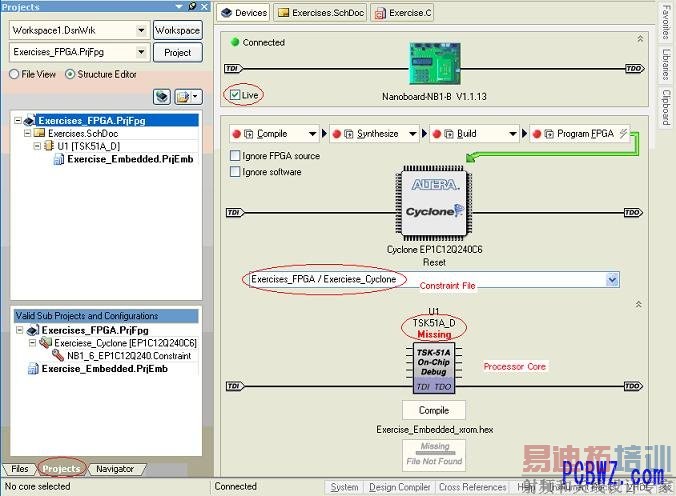

1、 按照系统设计的规则,将从集成库中拖拽出了器件连接构建一个完整的数字电路系统。然后选择[menu]Tools>>Annotate Quiet,系统将自动分配器件的标示,最后保存工程。特别应注意: 第二步,创建嵌入式软件工程: 2、 在工程栏中,用鼠标点击嵌入式工程名称,然后选择右键弹出[popus]Add New to Project>>C File。重新命名c文件名称并保存; 第三步,设定嵌入式软件工程选项: 4、选择Code Generation,选中Put strings in ROM only属性并选中中断向量属性及寄存器属性(图3.3),然后完成对嵌入式软件工程的环境设定。 第四步,设定微处理器的属性选项: 4、选择菜单[menu]Project>>Complier FPGA Project Exercises_FPGA.PrjFpg,在编译通过后保存;如图4.2在工程栏中选择Structure Editor属性,在工程栏窗口下将显示工程的结构层次关系,图中将显示出U1(TSK51A_D Processor)在设计中的位置关系;然后将嵌入式工程名称拖拽到U1上(如图4.2),从而在FPGA工程与嵌入式工程之间建立起相互关系; 第五步,FPGA的配置: 3、 在约束文件区,点击添加按钮,在弹出的文件打开对话框中,选择相应的约束文件名,点击打开,然后将配置管理器中,配置选项选中;(见图5.2) 4、在工程栏中,可以发现设置属性下将新添一个约束文件,(如图5.3)选择菜单[menu]Project>>Recomplier FPGA Project,保存FPGA工程。 最后,在系统控制面板上完成工程设计的全过程:

以上完成了从整个基于Altera Cyclone EP1C12型号FPGA项目工程的设计,通过将软硬件设计方案在NanoBoard NB1系统开发板上实际运行验证,再逐步优化,反复下载验证,最终完成项目的研发。 基本知识: 射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师... 天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:单片机

ARM

FPGA

嵌入式这些有什么区别,各自特点是什么? 射频和天线工程师培训课程详情>>

|