- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR2 DIMM 布线约束参考

录入:edatop.com 点击:

使用或参考本文件中的任何内容即表明您已经阅读、理解并同意文件末尾 重要说明 中的条款。

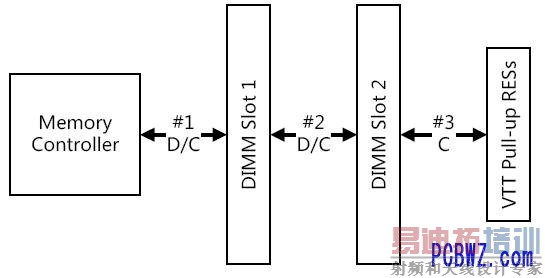

典型的DDR2 SODIMM应用拓扑结构由一个控制器,二个DIMM和VTT上拉电阻组成,如下图所示:

路径分成三段

路径1(#1): 控制器到第一条DIMM的路径,包括DQ/DQS信号、地址信号和控制信号。

路径2(#2): 第一条DIMM到第二条DIMM之间的路径,包括DQ/DQS信号、地址信号和和控制信号。

路径3(#3): 第二条DIMM到VTT上拉电阻的路径,只有地址信号和控制信号。数据信号有ODT。

约束以下关键长度

#1典型长度在 1900mil至 4500mil 之间。

#2 典型长度约为425mil左右。

#3典型长度在 200mil至 550mil 之间。#3丌需要时序约束。

同一个数据信号组(包括DQ及对应DQS)需要精确的匹配长度,长度差异要求在+/-50mil。其中分配给#1的长度差异要求在+/-30mil,分配给#2的长度差异要求在+/-20mil。

所有数据信号组的组间长度差异要求在+/-500mil。

地址信号间的长度差异要求在+/-200mil。

目标阻抗

推荐的布线目标阻抗为 50 Ohm。

适用范围

以上适用于JEDEC DDR2-400、DDR2-533、DDR2-667、DDR2-800。

重要说明:

1. 以上建议及数据均来自Mentor Graphics Hyperlynx 技术文件。

2. 本人不对以上资料持有任何权利,不对以上资料进行解释,也不承担应用过程中产生的责任及连带责任。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>