- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

SigXplorer中两种Buffer Delays 模式详解

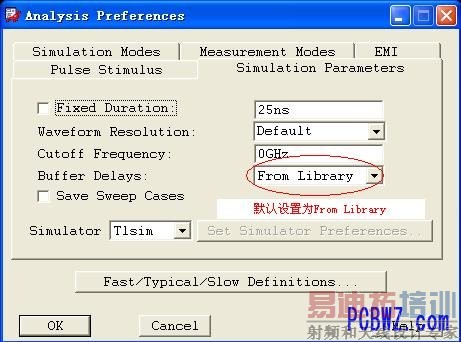

In SigXplorer, Buffer Delays Specifies how the simulator obtains buffer delays for the simulation. We can select one of the following options from the drop-down list:

*From Library: Specifies that the simulator obtain buffer delays stored with the model in the library. This is the default.

*On-the-fly: Specifies that the simulator measure buffer delays during circuit simulation and use these delays in the remaining calculations.

图1 Buffer Delay默认模式为From Library

那么,在时序仿真过程中,究竟该怎样设置这项参数?这两种模式有什么区别和联系呢?让我们看看下面的仿真实例。

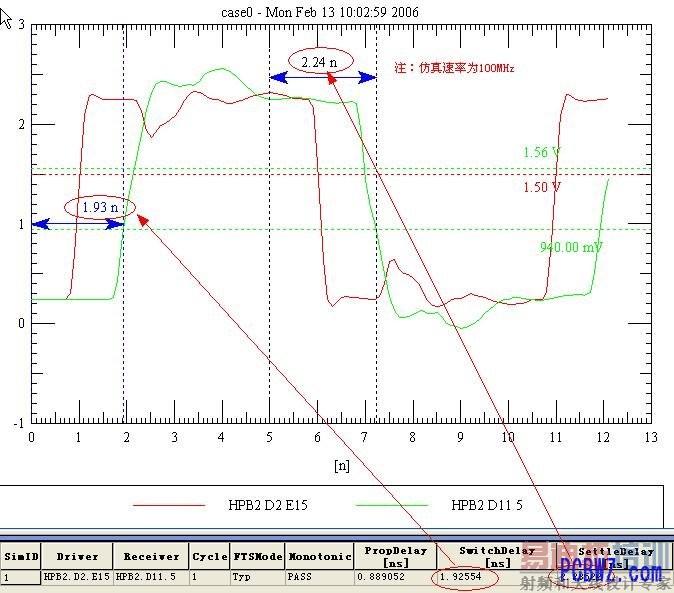

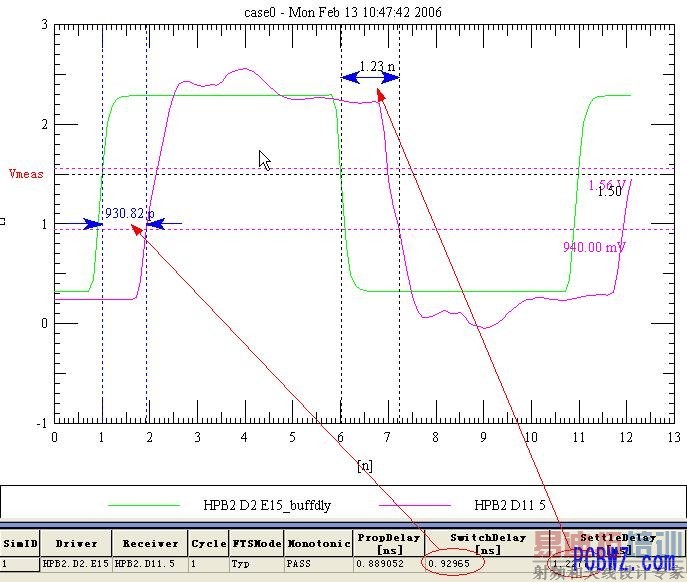

图2和图3分别显示了Buffer Delay模式设为From Library和On-the-fly时Switch Delay和Settle Delay的仿真数值。以Switch Delay为例,从这两个仿真图中可以看出二者的数值相差很大,差值为ns级别。通过观察仿真波形及仿真结果,可看出在From Library模式下,Switch Delay是从驱动器件输出Buffer上电开始测量的;而在On-the-fly模式下,是从驱动器件输出Buffer电压上升到Vmeas开始测量的。后者与我们所熟悉的常规定义相同,我们的时序公式也是基于此种定义推导的。所以在做时序仿真时应该选择On-the-fly模式。

如果我们将From Library模式下的First Switch Delay和Final Settle Delay分别记为Tswtich_lib和Tsettle_lib,On-the-fly模式下的First Switch Delay和Final Settle Delay分别记为Tswtich_fly和Tsettle_fly,则有Tswtich_lib = Tswtich_fly + Buffer Delay,Tsettle_fly = Tsettle_fly + Buffer Delay。即From Library模式下Switch Delay实际为On-the-fly模式下的Switch Delay + Buffer Delay。

图2 From Library模式下的Switch Delay和Settle Delay值

图3 On-the-fly模式下的Switch Delay和Settle Delay值

我们再来看看时序仿真过程中,Buffer Delays选择From Library模式会出现什么问题。

对于源同步来说,其理论时序计算公式如下:

Tflight_time_min > Thold-Tva_min +Tflt_clk@fast + Design Margin Fast 式(1-1)

Tflight_time_max < Tvb_min - Tsetup + Tflt_clk@slow -Tjitter - Design Margin Slow 式(1-2)

由前面推导知道,From Library模式下Switch Delay实际为On-the-fly模式下Switch Delay + Buffer Delay。以式(1-1)为例,From Library模式下,则其变化为:

Tflight_time_min + Tbuffer_delay > Thold-Tva_min +Tflt_clk@fast + Tbuffer_delay_clk + Design Margin Fast

可写为:

Tflight_time_min > Thold-Tva_min +Tflt_clk@fast + ( Tbuffer_delay_clk - Tbuffer_delay ) + Design Margin Fast

由上式得出,如果参考时钟和待仿真信号的输出Buffer模型相同,则它们的Buffer Delays相同,从而Tbuffer_delay_clk - Tbuffer_delay 为零,选择From Library模式对公式并没有影响,所计算结果也是正确的。所以对源同步来说,只要参考时钟和待仿真信号的模型相同,设置Buffer Delays为On-the-fly和From Library模式没有区别。但是如果参考时钟和待仿真信号的输出Buffer模型不同,则Tbuffer_delay和Tbuffer_delay_clk不同,这时所计算出的Tflight_time_min就有了误差,误差值为两个Buffer Delay之差值,可能为正也可能为负。虽然这个误差值不是很大,但是对于时序要求严格的网络还是会产生一定的影响。

对于共同时钟同步来说,由于其时钟由外部时钟提供,所以一般情况下公式两边的Buffer Delay值不会相同,因此选择From Library也会产生误差。

Tflight_time_min > Thold - Tcomin+Tflt_clk@fast(p_in_sd) + Tskew + Design Margin Fast 式(1-3)

Tflight_time_max < Clock Cycle Time - Tsetup - Tco max + Tflt_clk@slow(p_in_sd) - Tjitter - Tskew - Design Margin Slow 式(1-4)

终上所述,在做时序仿真时,应该注意选择Buffer Delays为On-the-fly模式。From Library模式只有在少数情况下可以应用。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...