- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

讯号路径设计讲座(2)探究千兆赫超高速ADC的系统高效能

对电路设计者来说,研发千兆赫系统要面临多方面的挑战 -- 也就是在处理千兆赫模拟频率和千兆样品取样率时,都会被要求非常精密的设计技术。这种系统的每个部分都需要透过精细的设计来达到最优化的效能,任何一个设计拙劣的模拟输入级或频率驱动电路和不恰当的布线,都将大幅缩减动态效能,而要在每秒钟数百兆位的频率下撷取数据,更是个让人头痛的问题。要达到高速度、高效能放大器或ADC的规格,需要具备多年的高速系统设计经验和精密的设计技术。

千兆赫超高速 ADC崛起之路

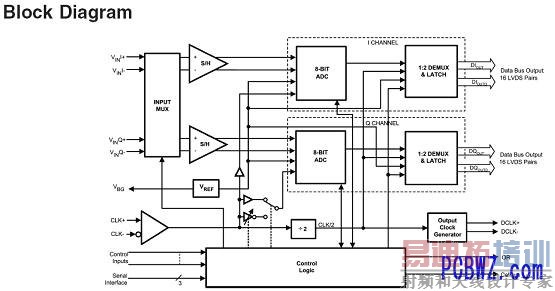

值得庆幸的是,现在设计者可以利用整合在全新的千兆赫超高速 ADC 组件中的许多优点,来简化系统的开发并缩短上市的时程。这种新类型的千兆赫模拟数字转换器,能实现通讯系统和量测设备的新架构。请见图1的ADC方块图。

图1:千兆赫ADC方块图

在研发千兆赫ADC系统时,必须克服三个最基本的难题。本文将探索这些难题,并提供对应的解决方案。

模拟输入驱动级

ADC要求一个能在不超过额定范围条件下将ADC输入驱动至满刻度的输入驱动级,这个输入级必须具备很宽的动态区间,提供耦合低失真的增益与(或)衰减,而此失真必须比ADC的谐波失真低。设计者有两个选择,RF变压器适用于AC耦合应用,但是DC耦合架构却需要一个差动放大器。新型千兆赫ADC组件就能轻松同时满足以上二者的要求。它的缓冲模拟输入简化了驱动输入的任务,而且不需一般用于ADC输入取样的RC极。

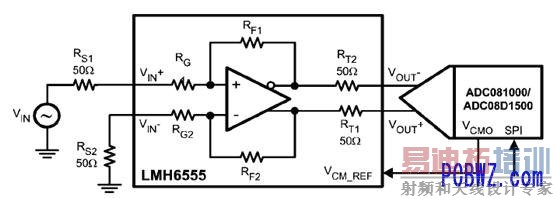

ADC输入端必需有一个精确DC共模电压;而当AC输入耦合模式被应用时,便会在芯片上提供此VCMO(共模输出电压)。在DC耦合模式中,VCMO接脚可用来设定输入讯号正确的DC模范共模电压。为逹到此目的,许多差动放大器都设有一个共同模式输出接脚,如图2所示。同时为了达到最大的动态效能,输入级必须能够驱动ADC至满刻度;输入满刻度的范围可选650 mVp-p或870 mVp-p,就像在操作正常模式下利用带有FSR(满刻度)控制脚位做出的选择一样。

在扩展的控制模式下,输入满刻度电压可设定为60 mVp-p到840 mVp-p范围中的任何值,使得驱动级的满刻度可以匹配ADC的输入区间并同时最优化动态区间。输入偏置电压可透过提供+/- 45mV 可调值的9位分辨率进行调整。ADC也设有过量输出来指示输入增益过大。图2展示了一个利用美国国家半导体LMH655X差动放大器系列执行的典型DC耦合。

图2:与新型千兆赫ADC组件耦合的差动输入DC

低抖动频率

高速度、高效能ADC要求一个非常稳定并带有最低相位噪声或抖动的输入频率讯号。ADC抖动的要求决定于ADC的分辨率、最大输入频率与相对于输入满刻度的最大输入信号震幅,允许抑制SNR中感应抖动的降低的最大抖动为︰

tJ(MAX) = (VIN(p-p)/VINFSR) x (1/(2(N+1) x π x fIN))

其中tJ(MAX)是在几秒钟内所有抖动来源的 rms总和,VIN(p-p)是峰至峰模拟输入讯号,VINFSR是ADC的满刻度电压,“N”是以位计算的ADC分辨率,fIN是最大输入频率。

另一项挑战是维持超高速频率的工作周期,因此新型千兆赫ADC组件可以选择将一个已校正工作周期的频率接收器作为输入频率周期的一部分。这种特性提供改善了的ADC频率,特别适用于双边取样(DES)模式。针对正常的和DES模式,此电路系统允许ADC以带有80 / 20 %工作周期比率讯号源来的频率。

注意:DES模式允许新型千兆赫ADC组件的其中一个输出端(I或Q通道)以两个ADC来取样,因此在一个频率周期,一个讯号输入就被取样两次,使整体取样率逹到输入频率频率的两倍,换言之, 1.5 GHz的输入频率便可提供3 GSPS的取样率。在这种模式下,输出是交叉存取的,因此数据进行有效的1:4讯号分离。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:实用电路设计讲座电源电路

下一篇:实用EMI噪讯对策技术讲座(13)印刷电路板