- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速电路的信号完整性分析

随着半导体技术和深压微米工艺的不断发展,IC的开关速度目前已经从几十MHz增加到几百MHz,甚至达到几GHz。在高速PCB设计中,工程师经常会碰到误触发、阻尼振荡、过冲、欠冲、串扰等信号完整性问题。本文将探讨它们的形成原因、计算方法以及如何采用IBIS仿真方法解决这些问题。

1 信号完整性定义

信号完整性(Signal Integrity,简称SI)指的是信号线上的信号质量。信号完整性差不是由单一因素造成的,而是由板级设计中多种因素共同引起的。破坏信号完整性的原因包括反射、振铃、地弹、串扰等。随着信号工作频率的不断提高,信号完整性问题已经成为高速PCB工程师关注的焦点。

2 反射

2.1 反射的形成和计算

传输线上的阻抗不连续会导致信号反射,当源端与负载端阻抗不匹配时,负载将一部分电压反射回源端。如果负载阻抗小于源阻抗,反射电压为负;如果负载阻抗大于源阻抗,反射电压为正。反射回来的信号还会在源端再次形成反射,从而形成振荡。现以图1所示的理想传输线模型为例,分析与信号反射有关的重要参数。

图1,理想传输线L被内阻为R0的数字信号驱动源Vs驱动,传输线的特性阻抗为Z0,负载阻抗为RL。如果终端阻抗(B点)跟传输线阻抗(A点)不匹配,就会形成反射,反射回来的电压幅值由负载反射系数ρL决定。Ρt可由式(1)得出:

ρL=(RL-Z0)/(RL+Z0) (1)

从终端反射回的电压到达源端时,可再次反射回负载端,形成二次反射,此时反射电压的幅值由源反射系数ρs决定,ρs可由式(2)得出:

ρs=(R0-Z0)/(R0+Z0) (2)

精确计算反射系数和反射电压的关键是确定传输线的特征阻抗,它不仅仅是印制线的电阻。当印制线上传输的信号速度超过100MHz时,必须将印制线看成是带有寄生电容和电感的传输线,而且在高频下会有超肤效诮和电介质损耗,这些都会影响传输线的特征阻抗。按照传输线的结构,可以将它分为微带线和带状线。

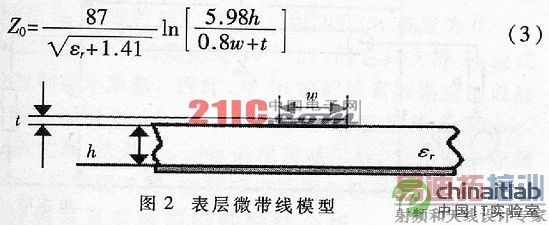

2.1.1 表情微带线的特性阻抗

微带线是位于接地层上由电介质隔开的印制导线,其模型如图2所示。印制导线的厚度、宽度、印制导线与地层的距离以及电介质的介电常数决定了微带线的特性阻抗。计算公式如下:

式中,Z0是微带线的特性阻抗(Ω),w是印制导线宽度(英寸),t是印制导线厚度(英寸),h是电介质厚度(英寸),εr是印制电路板电介质的相对介电常数。

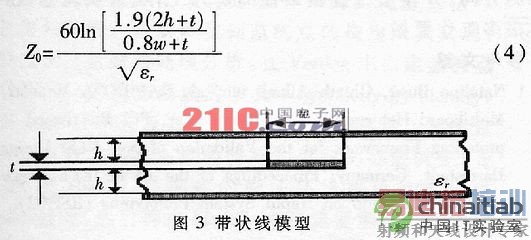

2.1.2 层间带状线的特性阻抗

带状线是介于两个接地层之间的印制导线,其模型如图3所示。它的特性阻抗和印制导线的宽度、厚度、电介质的介电常数以及两个接层的距离有关。特性阻抗的计算公式如下:

式中,Z0是微带线的特性阻抗(Ω),w是印制导线宽度(英寸),t是印制导线存度(英寸),h是电介度厚度(英寸),εr是印制电路板电介质的相对介电常数。

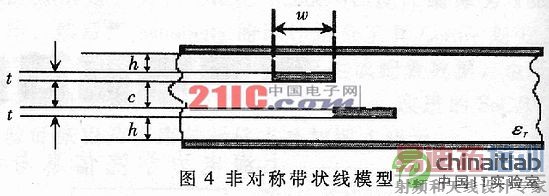

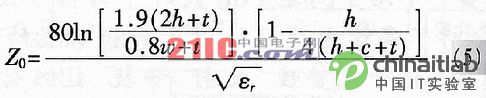

2.1.3 非对称带状线的特性阻抗

非对称带状线模型如图4所示。

特性阻抗的计算公式如下:

式中,Z0是微带线的特性阻抗(Ω),w是印制导线宽度(英寸),t是印制导线存度(英寸),h是电介质厚度(英寸),c是印制导线之间的距离,εr是印制电路板电介质的相对介电常数。

2.2 反射引起的问题及解决方法

由于存在传输线效应,从反射的角度来看,会出现以下信号完整性问题:

(1) 信号反射形成信号振荡。反射回来的信号会在源端和终端之间形成多次反射,加上传输线效应引起的过大的电感和电容,会导致信号振荡,即在一个逻辑电平附近上下震荡。这种现象尤其会出现在周期性的时钟信号上,从而导致系统失败。

(2) 信号反射会形成信号过冲和下冲。虽然一般来说每个信号的输入端都具有保护作用的齐纳二极管,但过程电平有效会远远超过元件电源电压范围,损坏元器件。

(3) 多次跨越逻辑电平门限。信号在跳变的过程中可能多次跨越逻辑电平门限,它是信号振荡的一种特殊的形式,即信号的振荡发生在逻辑电平门限附近,多次跨越逻辑电平门限会导致逻辑功能紊乱。

解决反射的根本办法是使信号具有良好的终端匹配,控制传输线的长度。同时也可利用IBIS仿真对系统信号进行优化。

3 串扰

3.1 串扰的形成和计算

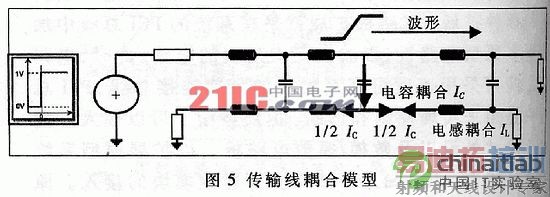

在高速信号系统设计中,反射属于单信号线现象,当然包括地平面问题。但串扰不同,它是两条信号线之间以及地平面之间的耦合,所以又称为三线系统。形成串扰的根本原因是信号变化引起周边的电磁场发生变化,特别是对于高速信号,信号的上升和下降沿的时间可以达到ps级,高频分量非常丰富,信号线之间的寄生电容和电感容易成为串扰信号的耦合通道。下面以图5所示的传输线耦合模型为例进行分析。传输线上分布着电感分量和电容分量,所以整个信号之间的串扰由两部分组成,即容性耦合干扰和感性耦合干扰。容性耦合干扰是由于干扰源(Aggressor)上的电压变化在被干扰对象(Victim)上引起感应电流从而导致的电磁干扰,而感性耦合干扰则是由于干扰源上的电流变化产生的磁场在被干扰对象上引起感应电压从而导致的电磁干扰。感性串扰和容性串扰的基本分析公式如下:

Xtalk(ind)=(Lm)/(Ra×Tr) (6)

式中,Lm是互感,Ra是干扰源的终端匹配电阻,Tr是信号上升沿的时间。

Xtalk(cap)=(Ra×Cm)/Tr (7)

式中,Cm是耦合电容,Ra是被干扰对象的终端匹配电阻,Tr是信号上升沿的时间。

3.2 影响因素

从上面的公式可以看出,串扰的大小与很多因素有关,如信号的速率、信号的上升沿和下降沿的速率、PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式等。

3.2.1 串扰线平行长度和间距对串扰的影响

印制电路板基材与两面的印制导线可看作一个电容器,其电容C可用平板电容器的计算公式来粗略地计算。

C=0.886εr(A/b)(pF) (8)

式中,A是两面导线重叠的面积(mm2),b是层压板电介质厚度(mm),εr是压板的相对介电常数。

当串扰信号线之间的平行长度增加时,将增加两传输线之间重叠的面积,所以线之间的耦合电容也会增加,从而增大电流串扰。同理,当传输线之间的间距减少时,两个耦合的传输线之间的耦合电容也会增加,从而增加串扰的数值。在高速电路设计中,重要的是减少串扰的数值,这样就要从结构上减小平行的长度,而且线间的间距也不能太小。

3.2.2 信号频率和沿速率对串扰的影响

在串扰效应中,除了信号本身的传输频率外,影响很大的还有信号上升时间和下降时间。在现代设计中,经常会出现几百兆赫兹的时钟信号和数字信号,这样信号的上升沿可以达到ps级。在这种情况下,信号的上升时间和下降时间对串扰的影响是不可忽视的。

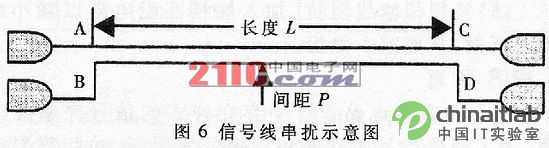

假设存在一个如图6所示的串扰模型。其中,两线的线宽均为w,两线的线间距为P,而两线的平行长度为L,如不特殊说明,w、P和L的取值分别为w=5mils,P=5mils,L=1.3inches,两线均为顶层微带传输线。PCB板的电介质电常数εr为4.5。分别在不同的频率和沿速率情况下对它进行仿真。干扰源信号的频率不同时。

在同样干扰信号频率(f=20MHz)下,不同干扰源沿速率所产生的信号串扰情况如图7所示。图中标记“1”和标记“2”箭头分别指被干扰对象的远端和近端串扰波形。

3.3 解决方法

从上面的分析来看,在高速电路设计中,除了信号频率对串扰有较大影响外,信号的边沿变化(上升沿和下降沿)对串扰的影响更大,边沿变化越快,串扰越大。所以解决串扰的方法主要从减少干扰源强度和切断干扰路径两个方面进行,有以下几个方法:

(1) 串扰与信号频率成正比,而且在数字电路中,信号的边沿变化(上升沿和下降沿)对串扰的影响最大,边沿变化越快变频分量越丰富,串扰越大,所以尽量少地使用dV/dt高的信号,在超高速设计中可以使用低电压差分信号或其它差分信号。

(2) 在布线空间允许的条件下,在串扰较严重的两条线之间插入一条地线或地平面, 可以起到了隔离的作用,从而减小串扰。

(3) 加大线间距,减小线的平行长度,必须时可以以jog(凹凸)方式走线。

(4) 对于信号速率比较高的信号,可以将它走线经过的微带线和带状线控制在地平面8mil距离内,这样可以显著减少串扰。

(5) 控制传输线阻抗,加入端接匹配电阻以减小或消除反射,从而减小串扰。

4 IBIS仿真

由于在高速电路设计中存在许多的信号完整性问题,为了确保产品的性能和缩短开发周期,迫切需要进行电路的板线仿真。仿真的手段主要有SPICE仿真和I/O Buffer Information Specification(简称IBIS)仿真等。IBIS模型只涉及器件I/O buffer的电气特性,不包含器件内核的结构、工艺和性能等信息,从而有效保护了IC开发商的知识产权,因此与SPICE模型相比,IBIS模型比较容易从器件生产厂家获得;同时IBIS仿真具有很高的精度,而且其仿真速度比SPICE仿真速速快25倍左右。本文只介绍IBIS仿真。

4.1 IBIS模型的组成要素

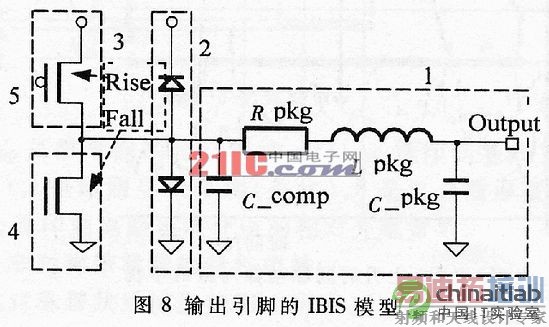

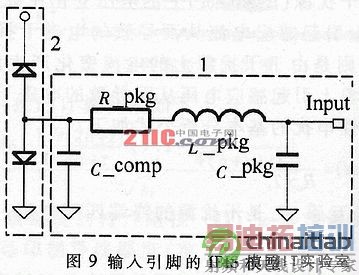

按器件引脚输入、输出性质的不同,IBIS模型中所包含的要素也不同。主要有两种,即输出引脚和输入引脚模型,图8描述的是输出引脚的模型。模块1表示自器件Pad到Pin的寄生参数,其中C_comp表示由输出Pad、钳位二极管引起的输出电容,L_pkg、R_pkg以及C_pkg表示由绑定引线和Pin引起的电感、电阻和电容。模块2表示器件内部的ESD保护二极管或钳位二极管,模块3表示开关管的开关动态特性,在模型文件中用dV/dt表示,决定信号的沿速率。模块4和模块5分别表示下拉开关管和上拉开关管,用模型文件中的V/I曲线表示。图9描述的是输入引脚的IBIS模型,它只包含模块1和模块2。

4.2 IBIS模型仿真步骤

由于IBIS仿真模型不但含有每个引脚的寄生参数,如封装寄生电感、电容和电阻,而且有表示信号沿速率的dV/dt和端口特征的V/I曲线,所以IBIS仿真具有精度高、仿真速度快的特点,被现在的EDA软件广泛采用,如Cadence和Mentor等。下面介绍Cadence软件的仿真步骤:

(1) 从半导体厂家获取IBIS模型。

(2) 进行IBIS模型的校正,这一步非常重要,因为有时候厂家提供的IBIS模型有错误。

(3) 在原理图设计时,将相应的IBIS模型赋予每个器件,然后进行PCB设计。

(4) 提取需要仿真的每个网络的拓扑结构。

(5) 在源端加上仿真激励,然后进行仿真。如果存在信号完整性问题,可以修改张端匹配或PCB设计,然后再进行仿真,直到满足信号完整性要求。

信号完整性设计已经成为高速PCB设计中非常重要的一环,需要从原理图设计开始进行考虑,并采用IBIS仿真加速设计的进度和保证设计的成功。当然由于IBIS模型不涉及到IC内部的晶体管结构,同时对外面的被动器件和结构(如过孔)描述不够精确,所以对于超高速PCB(信号传输速率超过1Gb/s)的设计,可以采用SPICE仿真,同时采用三维电磁场提取过孔的SPICE模型。限于篇幅,本文没有讨论这些问题,可参考相关文献。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB加工之蚀刻质量及先期问题分析

下一篇:PCB电子元件如何应对高功率电平?