- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

电子产品设计中的信号完整性问题,随着速率提高日益严重。

录入:edatop.com 点击:

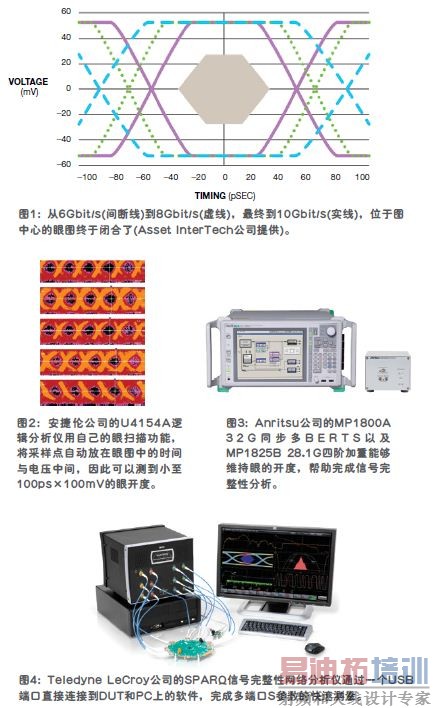

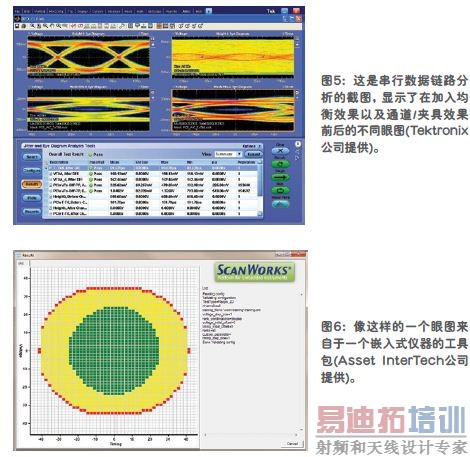

. 向更高速和更高信号频率的每次新进步,都使总线对信号失真和异常更加敏感,这些异常可能破坏吞吐量并造成系统堵塞。“并行化的串行”标准对信号完整性问题影响甚大。众所周知,极高速电路很难检测。 . 一种方法是用光背板来改善信号自身路径;另一种改进信号完整性的方法是用均衡方法来修饰信号,尽量减少串扰。 . 很多设计人员对信号路径采用更好的设计实践经验,控制串扰和EMI。 . 大多数致力于信号完整性问题的工程师都同意,对于高速系统设计而言,仿真正在成为必需。 电子设计趋势推升了设计的复杂度与速度,如多个高速总线的使用,因此带来了新的信号完整性挑战。有鉴于此,EDN邀请了一些做信号完整性工作的工程师召开了一次虚拟座谈会,探讨当前的危害情况,评估现有测试设备能在多大程度上符合要求,并确定如何从短期和长期两方面改善信号完整性问题。当然,很多东西都会影响到信号完整性(参考文献1)。在本次讨论中,我们主要关注串扰与EMI(见附文:关注DESIGNCON上的信号完整性)。 问题何在? 很多有经验的人都注意到了多个高速总线对信号完整性的影响,以及如何避免相关的问题。Tektronix公司高级技术与营销经理Chris Loberg与AssetInterTech公司设计验证与测试副总裁Tim Caffee都认为,高速总线上工作裕度的缩减是这些挑战的来源。 Loberg认为:“设计趋势是更快的串行速度,超过10Gbit/s,没有新的高性价比架构能够改善信号路径的适应性问题,如对EMI和串扰。因此,必须做像均衡这样的信号调节,以尽量减少EMI与串扰的影响,让接收器能够精准地确定串行总线的逻辑变换。” Loberg注意到,1或0变换之间的间隔时间正在不断缩小,因此,在传统上用于变换评估的眼图中,EMI与串扰正在使眼“闭合”。工程师们不再能够有效地评估信号完整性问题,因为对交越点与时序完整性的评估已变得更加困难。 Caffee指出,高速总线每发展一代,工作裕度都随信号频率的增加而缩减,产生了诸如抖动、符号间干扰(ISI )以及串扰等影响,对高速SerDes与存储器通道的信号完整性是一种浩劫。速度和信号频率每提高一步,总线都会对失真与异常更为敏感,可能导致流量的中断或系统堵塞。 图1中的眼图展示了这一点,图中显示了不断增加的信号频率对三代假想高速总线的作用及结果,即缩小了总线上的工作裕度。随着频率的增加,即使最轻微的失真也可能损及信号的吞吐量。 Teledyne LeCroy公司信号完整性产品经理Alan Blankman相信,更高的码率(>25 Gbit/s)以及“并行化串联”标准(如PCIExpress、40/100Gbase-R和InfiniBand)都是引起现在信号完整性问题的原因。他说:“更高码率要求较高频率成分有更快的边沿,这样,在连接器、过孔、封装等阻抗失配处就会产生更大的反射,会有更高的损耗以及更多的串扰与EMI产生,因为增加了与邻近走线的耦合。” 安捷伦技术公司信号完整性计划经理Shamree Howard补充说,较高的速度还给精确的数据捕捉带来了麻烦,因为它需要精准的触发。她认为,抖动的测量是确定高速数据链接特性的关键,并指出:“抖动的测量是很复杂( 即使给用户提供了某种一键界面),它要考虑时钟恢复及锁相环知识、抖动分解技术及其假设、串扰及其影响,以及不同的波形统计分析方法等”(参考文献2)。Howard补充说,安捷伦的U4154A4-Gbit/s AXIe逻辑分析仪可以对小至100ps×100mV的眼开度做出可靠的测量(图2)。 SignalConsulting公司的Howard Johnson也同意这点,大家都知道极高速电路很难检测。Johnson说:“即使有这么一种可以完成任务的探头,我们通常也没办法把它放到待测电路中的某个点上。”他建议采用协同仿真方法,或同时开发物理电路及其软件仿真的方法。 Ransom ’s Notes 公司的Ransom Stephens注意到,尽管领先制造商拥有新的示波技术,但现在仍然没有能明确地识别串扰的自动方法。最新测试产品提供了以误码率(BER)评估串扰作用的方法,但它们全都是采用排除法。 Stephens承认:“避免串扰的原理虽简单,但实际上有时是不可能的。”当一个干扰信号做逻辑变换时,震荡的辐射就造成了串扰,因此增加上升/下降时间能减少串扰。由于串扰就是一种干扰,因此增加走线间距也有很好效果。 Stephens建议:“不过我觉得,细心的差分设计是最佳措施。如果你真能让差分偏移降下来,让两根走线几乎完全相互依靠,那么差分信令就有好的机会来抑制串扰。” 如何改善SI? Tektronix公司的Loberg认为,我们有几个方法。首先就是改变和增强信号本身的路径。一个办法是采用光学背板。这个办法正在逐步实现,但并非主流(想想Thunderbolt)。另一个改善信号完整性的方法是用均衡方法去修改信号,来尽量减少串扰。例如,可以对芯片做硬编码,或编译FPGA的代码,实现信号均衡。另外,很多设计者通过对信号路径的更好设计,来控制串扰和EMI 。 Asset InterTech公司的Caffee建议工程师在系统生命周期的每个主要阶段(从设计到现场运行),都要对总线的信号完整性做验证,不过他也承认这是一个具有挑战性的工作,因此不是一个普遍的方案。如果在原型板制造期间发现问题,则可能造成设计的变化;如果是在生产期间发现问题,则可能改变生产工艺。如果是在现场发现问题,则要对性能不良的系统、设计做查错,下一代产品应做设计变更,生产工艺变更,以减少退货和保修问题。 Anritsu公司业务发展经理HiroshiGoto建议将预加重作为一种有效的传输技术,以保持眼图的开度。当传输速度增加到20Gbit/s甚至更高时,Goto建议采用一种3阶或4阶加重信号,以增加被加重的位数。 但是,要对每一阶检查与设定加重率的组合,这也是一个复杂的工作,在没有定量指导情况下,难以找到理想的加重信号。 Goto称,Anritsu开发了MP1825B四阶加重与传输分析软件,与MP1800A信号质量分析仪B E R 测试套件(BERTS)一起使用,能根据待测设备(DUT)的“反相特性而找到理想的加重设置”(图3) 。“这提升了眼的高度,维持了眼的开度,从而能在最短的时间内做出更好的定量信号完整性分析。” 仿真与验证 大多数人都同意仿真正在成为高速系统设计的必需。安捷伦公司的Howard称该公司的先进设计系统(ADS)是用于高速数字应用的领先EDA软件。 Teledyne LeCroy 公司的Blankman补充说,要检测和减少串扰问题,设计人员必须能通过仿真方法,预测到近端和远端串扰,并用测量来验证仿真中采用的模型(图4)。在验证串扰模型时,设计人员要测量多个差分通道的S参数(对干扰源-受扰者模型是8个端口,对干扰源-受扰者-干扰源模型是12个端口,或者甚至有更多的端口数)。 串扰的测量需要用实时示波器做垂直噪声测量,这种设备可以从串行数据信号中提取出串扰。这些测量应评估作为BER函数的眼图闭合度,如抖动测量那样。当然抖动测量也很重要。如同时测量抖动和噪声,则获得的串扰图像要比单独测量抖动更加复杂。 工具箱 测试设备供应商正在努力发展自己的工具,以确定抖动的特性,改善信号完整性分析,因此对信号完整性工程师而言,最好的工具箱可能尚未出现。Signal Consulting的Joh nson预计,“下一个趋势会是发展一种专用设备与测试软件的混合体,目的是确定一个电源系统的特性,并为电源系统注入特定的测试电流波形。”Ransom’sNotes的Stephens建议我们密切关注更多的串扰均衡技术。 那么,我们现在有什么? 示波器。这里是大带宽示波器真正展示自己价值的地方。Teledyne LeCroy的Blankman说,非归零(NRZ)串行数据样式的上升时间不到30ps。他指出,测试PCIe Gen3系统的接收器需要一台13GHz带宽的示波器,而发射器测试则需要20GHz的示波器。 Blankman 称:“新兴的多路设计甚至需要更多的通道数和带宽,如InfiniBank和40/100GBase-R。这些标准的码率达25Gbit/s和28Gbit/s。一般要求示波器频率为基频的四或五倍,即50 GHz~ 65 GHz 。由于InfiniBan k与40/100GBase-R是多路的,因此一次要有8、12甚至更多的通道,才能完全确定SI问题的特性。”Blankman称TeledyneLeCroy的LabMaster 10 Zi带宽可达65GHz,并有一个ChannelSync架构,可使最多80个通道同时在一台仪器上工作。 网络分析仪。对于确定多路系统的串扰特性,以及揭示DUT的频率特性,网络分析仪很重要。Anritsu公司的Goto指出,为了获得最佳S参数数据,矢量网络分析仪应扩展其频率的覆盖范围。他推荐Anritsu的VectorStarVNA,其频率区间为70kHz~125GHz。 他警告说:“虽然频率上限最受人关注,但一定要记住,在信号完整性应用中,对最低可能频率的精准测量才是关键。通常情况下,测量尽可能靠近直流可以改善模型精度,因为它提供了有助于建立一个高精度眼图的精密数据。” Blankman指出,大端口数的网络分析仪可能很昂贵。他说TeledyneLeCroy的SPARQ系列网络分析仪(图4)用于信号完整性测量,提供了一种传统VNA的较低成本选择。(SPARQ意为“快速S参数”。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:第二代高速串行总线,那些让人讨厌的问题

下一篇:液晶模块PCB板回流焊作业指导书

射频和天线工程师培训课程详情>>