- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

1600Mbps DDR3 高速信号仿真和PCB设计

设计简介

Memory部分的电路板设计在系统设计中占有重要的地位,目前Memory速度被一再提升,DDR3的速度已经高达1600Mbps,数据脉冲宽度只有625ps,对信号的质量和时序都提出了更高的要求,同时也增加PCB设计需要考量的参数。

线路板设计参数

该线路板设计采用Memory Down结构,一共4片SDRAM,设计速率1600Mbps,设计的走线阻抗控制,线宽线距以及等长要求可以由SI仿真评估确定。

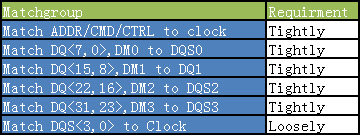

1.等长分组处理

DDR设计采用分组等长的策略,分组可以更好的控制时序要求,简化pcb layout难度,在pcb布线允许的情况下,也常常采用一起走做等长的处理方法,结果是一致的。

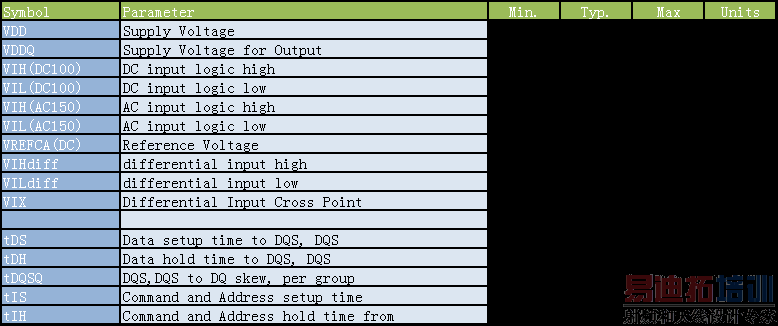

2.SI仿真需要的DC,AC及时序参数

下图展示的DDR3 SDRAM在SI仿真处理中所需要的部门时序参数,DDR3部门的时序分析涉及参数较多,在高速度下,可以用于时序余量计算的时间余量很有限,所以每个参数都要慎重考虑。

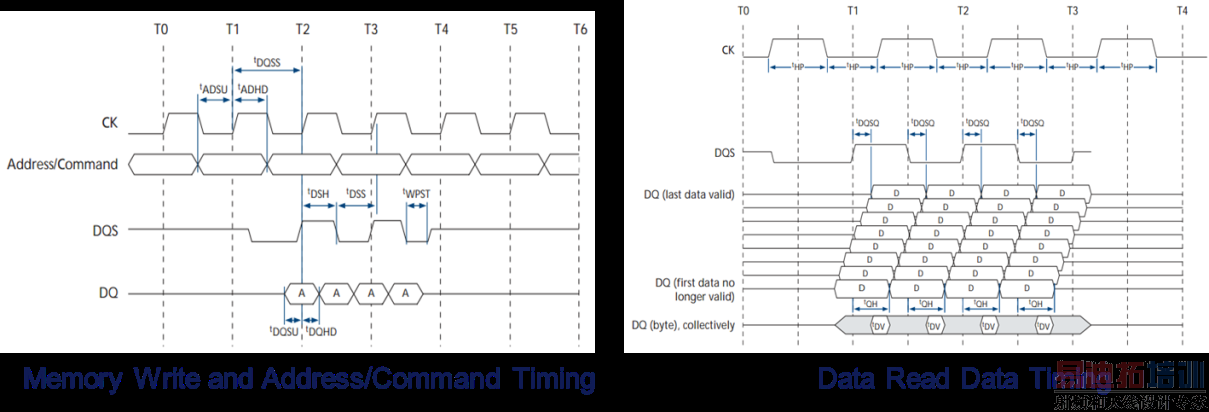

[p]3.时序计算参考

DDR3在满足信号质量的前提下,还必须满足时序要求。DDR3采用的是源同步系统,在工作时必须保证(DQ, DQS, Clock)、(Address/Command,Clock)、(Control,Clock)之间的时序关系,DDR3的时序余量分析是前期设计中很重要的一部分。

项目挑战

Memory高速电路板设计速度较高,客户在所有的信号线上都添加了终结匹配电阻,由于板子区域有限,匹配电阻无法放到有效地区域(靠近驱动端),而且大大的增长了PCB布线的长度,0.4mm BGA管脚间距的PCB设计和生产加工难度很大。通过SI仿真评估,建议客户拿掉DQ<31:0>上的所有匹配电阻,Wrtie时使用DDR3的odt功能做信号匹配,Read时通过调节DDR3的输出阻抗,做到自匹配,从而不仅有效的解决了线路板布线的难度,走线变短,同时也提升了整体信号的质量。

客户反馈

目前此板 PCB设计、PCB制板、器件采购、PCBA贴片一次性成功。

优化建议

在SDRAM的clock pin处添加终结电阻,改善Clock的信号质量。

SI仿真展示

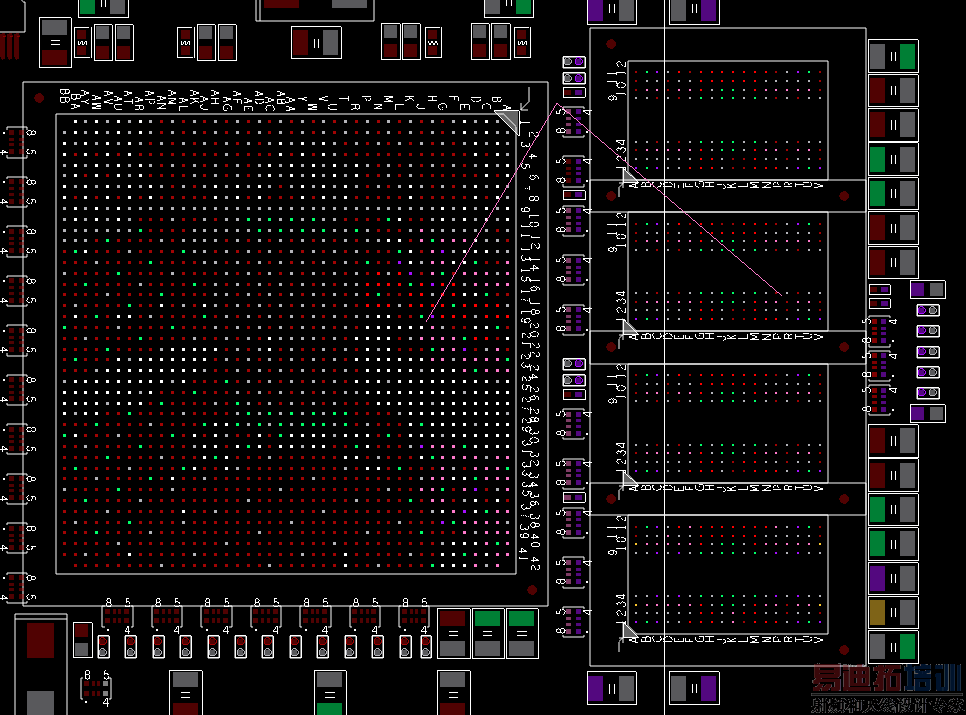

1.pcb layout布局图

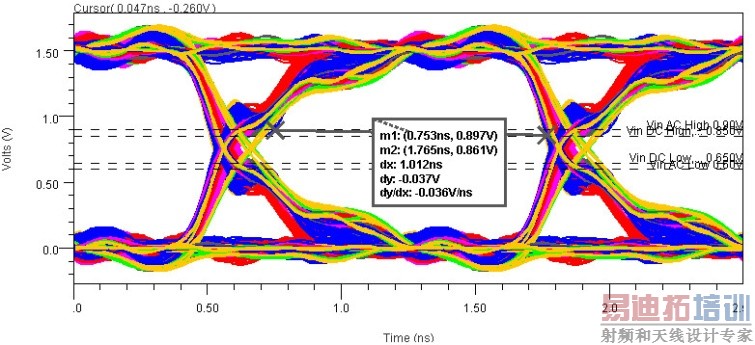

[p]2. address Group eyes

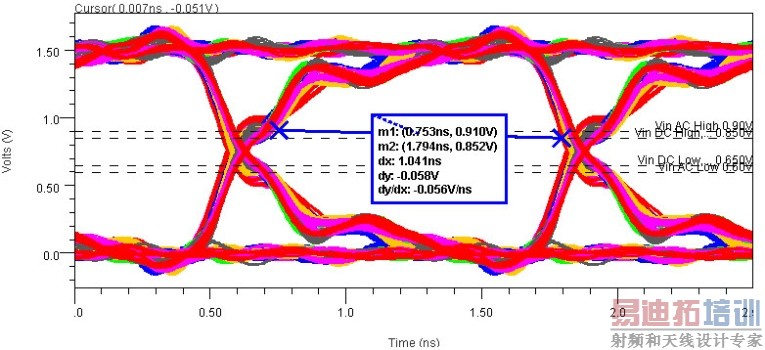

3.Control Group eyes

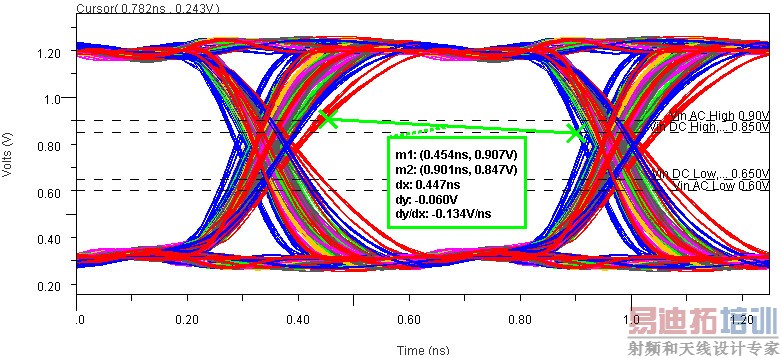

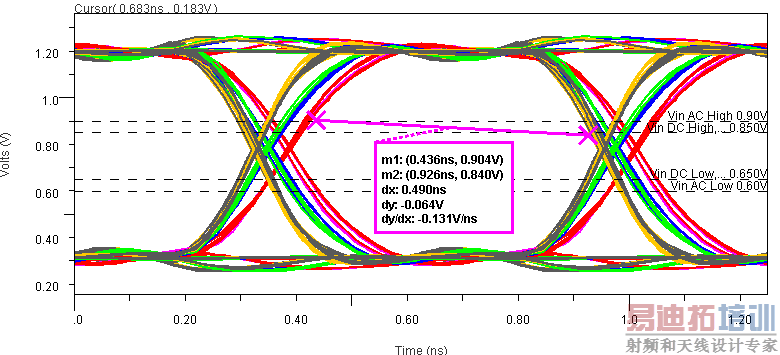

4.DQ Write eyes

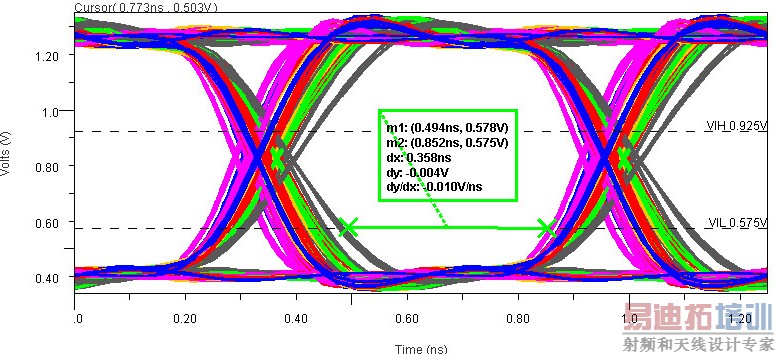

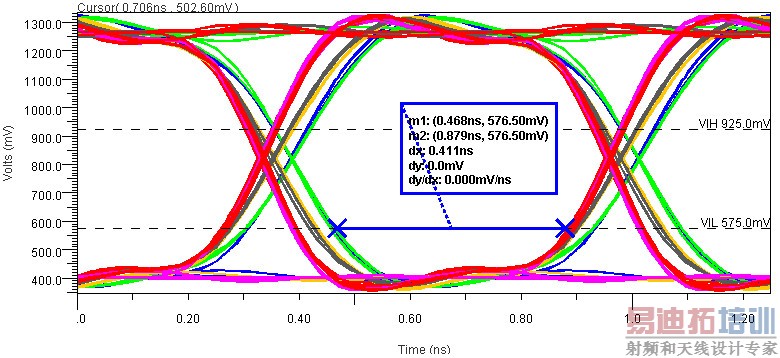

5. DQ Read eyes

6.DQS Write eyes

7.DQS Read eyes

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:EMC设计的基本概念

下一篇:PCB设计基础知识1