- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR3总线信号完整性测试需要关注4点

DDR3总线信号完整性测试需要关注4点

上周五到客户处介绍DDR3信号完整性测试方案,惊讶之处是他们不仅不知道DDR3总线信号完整性测试要点,而且受某些供应商的引诱,准备购买2.5GHz的示波器来测试DDR3 1.33G总线。

商业市场上,我坚信诚实做事,踏实做事,细致做事,一定会带来长久的生意和回报,就像我们在华东的国防生意一样。

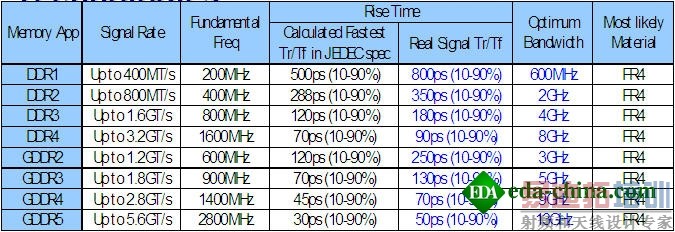

那么DDR总线的测试实际应该需要多少带宽的示波器(最小要求)?

因为Jedec规范没有给出最快的上升/下降时间,下表是基于芯片的分析和实际的情况得出的结果:

当正确选择示波器后,我们测试DDR3总线需要关注4点:

1. 探测

如何正确的探测是测试DDR3的难点所在。

针对嵌入式系统,建议在PCB设计过程中,做可测性设计,即规划好准备测试那些信号,然后留出测试点(包括测试点附近的接地点),测试点要尽量靠近DRAM IC管脚处,因为Jedec规范的位置是BGA焊球的位置。

另外一种方法是使用BGA探头适配器(前面文章有介绍),这是最可靠的方法,但是加工是其难点。

针对计算机系统,建议使用BGA探头适配器加工几条DIMM供测试使用,或使用ZIF探头附件焊接几条DIMM供测试使用(这种方法,现在用的比较多)。

2.读写信号分离

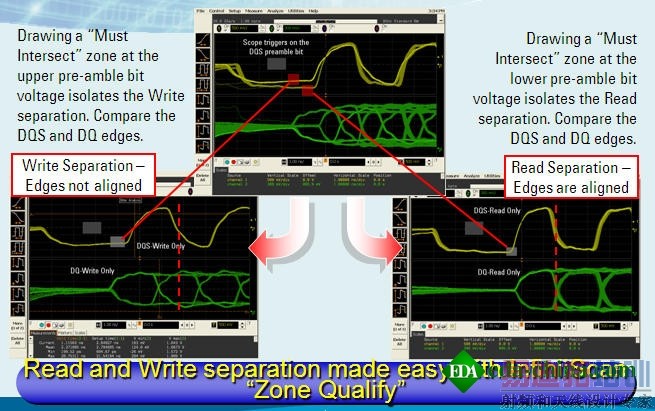

DDR总线需要测试时钟、命令/地址、数据等,数据测试是难点,而关键参数是建立时间和保持时间,所以需要对读写信号进行分离,分离后分别测试读和写信号的建立时间和保持时间。

现在大多读写分离的方法是使用示波器捕获大量数据,然后根据建立时间和保持时间的关系,从波形中间找到那些段波形是读,哪些段波形是写,然后再分别测试出读写的建立时间和保持时间,以及其他参数。如果用手动量测的话,这种方法需要花费大量时间,但是仍然不能解决测试数据量不够的问题。

使用InfiniiScan是一种较好的方法,它使用画图式的图形触发分离出读和写,然后再累积成眼图,可以累积大量的数据,然后再测试建立时间、保持时间和其他参数,分离方法如下图:

3. 自动化一致性测试

因为DDR3总线测试信号多,测试参数多,测试工作量非常大,如果不使用自动化的方案,按Jedec规范完全测完要求的参数可能需要1到2周的时间。而自动化测试软件可以帮助解决测试工作量的问题,正确使用的话,可以把测试时间从1-2周缩小到1-2天。

所以,建议使用自动化测试软件,这是提高效率的一种方法。

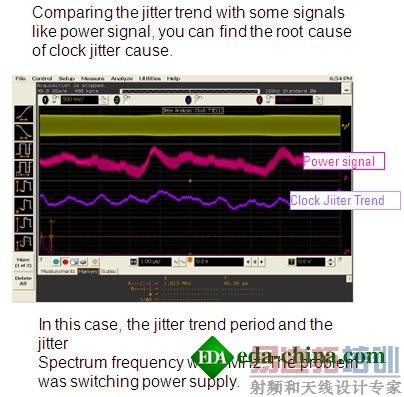

4. 调试

对于系统,出现时钟问题时,很多时候与供电电源有关(约占80%以上),这时候可以使用抖动分析软件抖动趋势图方法进行问题根源跟踪:因为抖动趋势图和其他通道信号可以同时显示在示波器的屏幕上,当发现抖动趋势图和电源信号同步变化时,基本可以确定抖动问题是来自这个电源。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB模拟设计--------单独的模拟地和数字地

下一篇:PCI接口布线特殊要求