- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用Vivado-HLS实现低latency 除法器

1 Vivado HLS简介

2创建一个Vivado-HLS工程

2.1打开Vivado HLS GUI

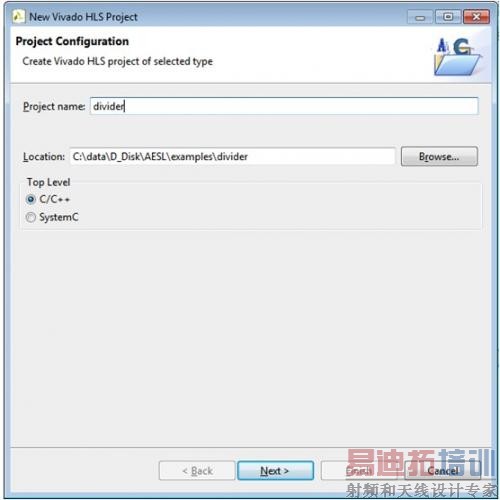

2.2创建新工程

在 Welcome Page, 选择Create New Project

2.3添加源文件

指定顶层需要综合的源文件名,并添加文件.

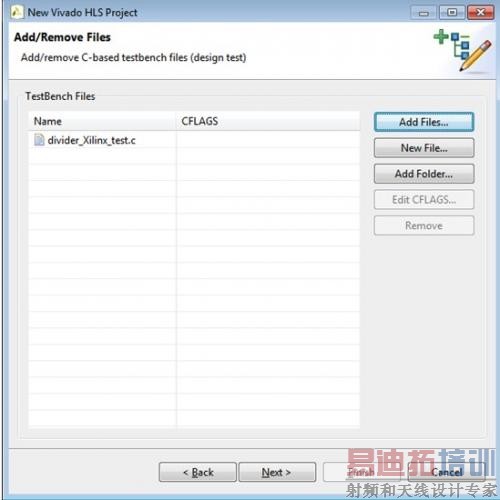

2.4添加测试文件

添加测试文件.

2.5创建solution

3 C Validation

4 C Synthesis. 13

5 Explore不同新的Solution. 15

1 Vivado HLS简介

Xilinx Vivado High-Level Synthesis (HLS)工具将C, C++,或者SystemC设计规范,算法转成Register Transfer Level(RTL)实现,可综合到Xilinx FPGA.

将DSP算法快速转到RTL FPGA实现将C至RTL时间缩短4倍基于C语言的验证时间缩短100倍RTL仿真时间缩短3倍

2创建一个Vivado-HLS工程2.1打开Vivado HLS GUI双击桌面上Vivado HLS GUI图标,或从Start > All Programs >

Vivado > Vivado HLS GUI

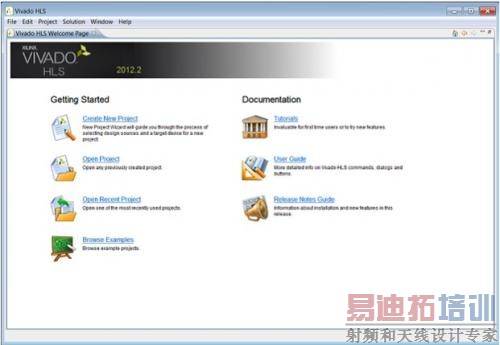

打开GUI之后,Vivado-HLS welcome界面如下所示:

2.2创建新工程在Welcome Page,选择Create New Project

2.3添加源文件指定顶层需要综合的源文件名,并添加文件。

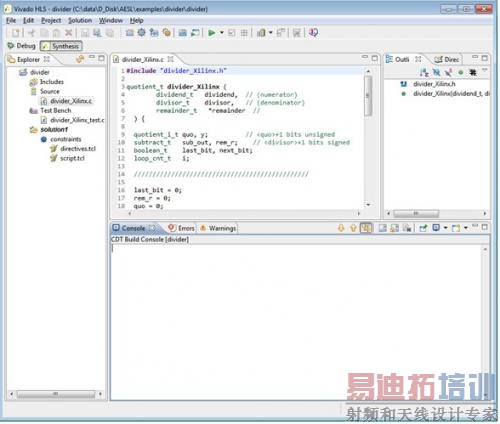

本除法器设计采用移位算法

#include "radix2div.h"

quotient_t radix2div (

dividend_t dividend, // (numerator)

divisor_t divisor, // (denominator)

remainder_t *remainder //

) {

#pragma AP latency max=3

#pragma AP pipeline

quotient_i_t quo, y; // +1 bits unsigned

subtract_t sub_out, rem_r; // +1 bits signed

boolean_t last_bit, next_bit;

loop_cnt_t i;

///////////////////////////////////////////////

last_bit = 0;

rem_r = 0;

if (LOOP_MAX > 32)

quo = 0ULL;

else

quo = 0;

//////////////////////////////////////////////////

div_booth_label0: for (i = 0; i

#include

#include "radix2div.h"

//////////////////////////////////////////////////////////////////////////////

quotient_t radix2div (

dividend_t dividend, // (numerator)

divisor_t divisor, // (denominator)

remainder_t *remainder //

);

//////////////////////////////////////////////////////////////////////////////

int test_divider (dividend_t dividend,

divisor_t divisor

)

{

quotient_t quotient;

remainder_t remainder;

quotient = radix2div(dividend,divisor,

fprintf(stdout, ">>>>>>>>> dividend = %u, divisor = %u quotient = %u remainder = %u n",

dividend, divisor, quotient, remainder);

fprintf(stdout, ">>>>>>>>>—— n");

if ((quotient == dividend/divisor) (remainder == dividend-(divisor*quotient)) ) {

printf ("PASS n");

}

else {

printf ("FAIL n");

return 1;

}

}

//////////////////////////////////////////////////////////////////////////////

int main () {

int i, j;

dividend_t max_num;

max_num = 0;

j = LOOP_MAX-1;

for (i = 0; i < j; i = i+1) {

max_num = max_num + pow(2,i);

}

[p]//////////////////////////////////////////////////////////////////////////////

test_divider (max_num,1);

test_divider (2,pow(2,9)-1);

test_divider (max_num,pow(2,9)-1);

test_divider (8,1);

test_divider (99,10);

//////////////////////////////////////////////////////////////////////////////

test_divider (max_num,1);

test_divider (2,pow(2,9)-1);

test_divider (max_num,pow(2,9)-1);

test_divider (8,1);

test_divider (99,10);

}

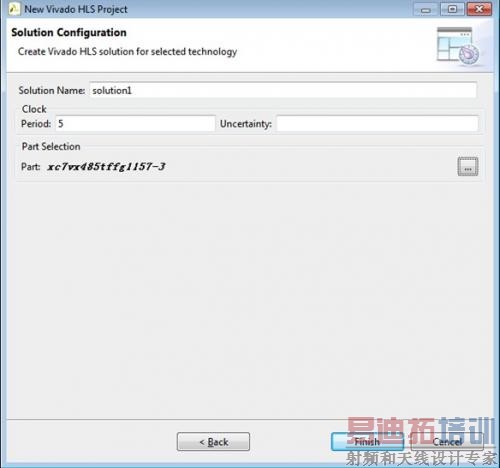

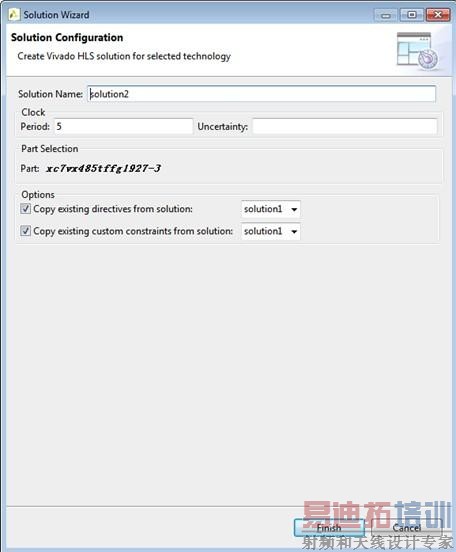

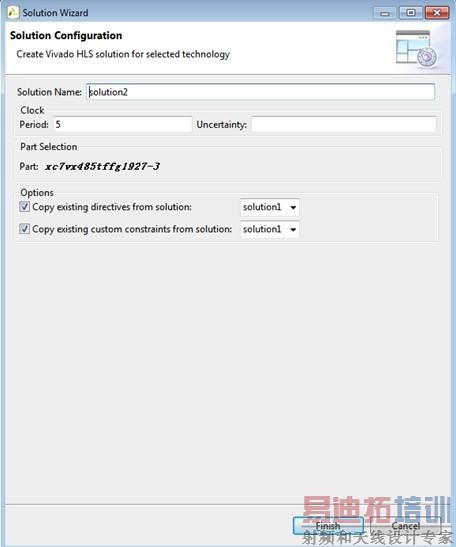

2.5 创建solution

创建solution, 时钟约束, 并选器件.

打开包括工程信息Vivado HLS GUI.

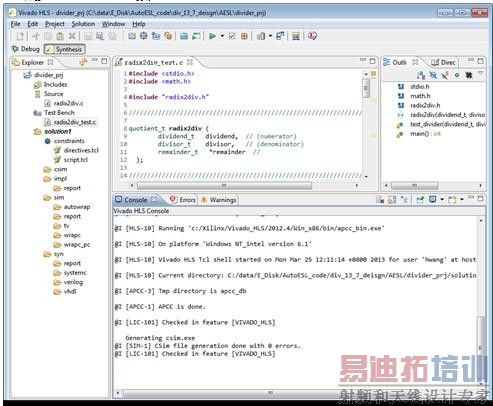

3 C Validation

在将c/c++/system c 转换成RTL之前,必须先验证C 设计,确保其功能是正确的

点击 "Run C Simulation" 图标,

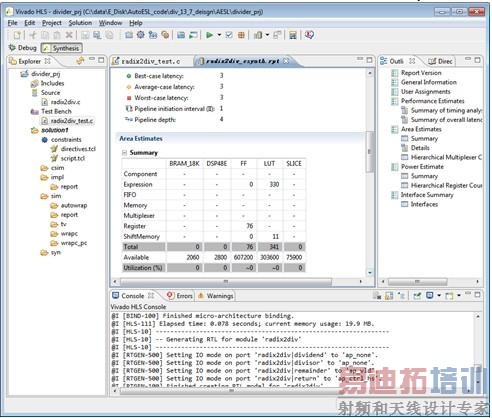

4 C Synthesis

现在可以对设计做C 综合,生成RTL代码. 当综合完成,, GUI 更新综合结果. 包括资源使用,latency等。

为了达到了预先要求为3 个时钟周期, 将latency 的directive设置为3。

5 Explore 不同新的Solution

project -> new solution。

在同一个工程里面,可以使用同一套源代码,进行不同solutions的尝试。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...