- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

MATLAB 算法面向 FPGA 的浮点定点转换

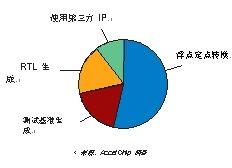

AccelChip 公司(最近已被赛灵思公司收购)最近所做的一次调查显示,53% 的回答者认为浮点定点转换是在 FPGA 上实现算法时最困难的地方(图 1)。

虽然 MATLAB 是一种强大的运算开发工具,但其许多优点却在浮点定点转换过程中被降低了。例如,由于定点算术中精度较低,新的数学误差被引入算法。您必须重写代码,使用能够反映实际硬件宏架构的低级模型来替换高级函数和运算符。而仿真运行时间将可能长达 50 倍之久。基于这些原因,MATLAB,这一算法开发的优势选择,却经常遭到遗弃,转而使用 C/C++ 进行定点建模。

生成定点模型

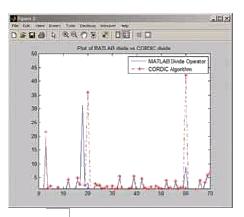

如果未将高级函数和运算符替换为硬件精确的宏架构,浮点 MATLAB 算法的定点表示将不会真正反映最终硬件的响应(图 2)。

图 3 对此进行了突出显示,该图使用一组量化为 8 位有符号二进制补码的随机输入矢量,对 MATLAB 除法运算符与工具硬件 CORDIC 除法算法的定点响应进行了比较。 根据数据数值,计算输出之间将存在巨大分歧。

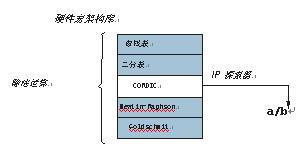

在定点生成过程中,AccelDSP™ Synthesis 综合工具的 IP Explorer™ 技术将自动使用硬件精确的表达式替换高级 MATLAB 函数和运算符(图 4)。此步骤是透明的,且不需要对 MATLAB 代码进行修改。您可以使用综合指示来重新定义初始宏架构和微架构选择。

一旦这些运算符替换为硬件精确的宏架构,量化过程就将开始。

图形辅助式自动量化

与定点 DSP 处理器不同, FPGA 结构允许使用可变定点字长。通过解除对变量的固定 16 位或 24 位边界限制,您可以执行需要位数增长的算术计算而不会引起额外的数值误差。

这对于像雷达、导航和制导系统等要求较高数值精度的应用来说是一个巨大的优点。

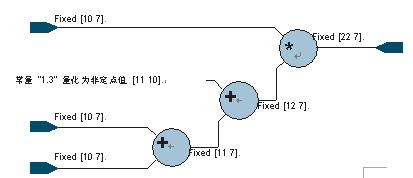

在大多数情况下,位增长率定律 (bit growth rules) 是简单直接和易于理解的。例如,一次加法的结果增长一位,而一次乘法的结果则增长到等于输入字长度的总长度(图 5)。然而,要在实际设计中确定变量的这些属性,将是一个高度反复的过程。允许未检查的位数增长现象发生,在硬件中代价是昂贵的,通常也是不必要的。如果您技术功底深厚,您可以采用各种技巧来尽可能地减小字长而同时保持数值精度。

确定变量的初始量化值和随后对该值的细化改进的过程,非常适合自动化。AccelDSP Synthesis 综合工具包括自动化浮点定点转换,该功能将在仿真过程中对浮点 MATLAB 模型进行分析,以确定输入数据和常量的动态范围要求。这些值提供了自动量化过程的起点,然后该过程将利用从 6,000 多个设计中获得的大量内置经验,确定下游变量的最佳字长。

通过自动量化而获得的初始定点模型提供了一个良好的起点,但一般需要对该模型进行细化改进。

图 1 – AccelChip DSP 设计挑战调查

图 2 – 替换内置运算符和函数

图 3 – MATLAB "/" 与 CORDIC 的定点响应比较

图 4 – 自动硬件精确 IP 插入

图 5 – 定点位增长

MATLAB 提供了一种开发算法数学模型的高效环境,这种算法通常只需使用一组较少的仿真矢量就可完成

该过程高度反复,且紧密耦合至数据作用 (data effect) 的分析。为了最大程度地缩短这一反复循环时间,AccelDSP Synthesis 综合工具提供了一种加速定点仿真流程。

图 6 – FFT 示例仿真运行时间

分析定点数据作用

MATLAB 提供了一种开发算法数学模型的高效环境,这种算法通常只需使用一组较少的仿真矢量就可完成。但是,当把该算法应用到定点硬件时,您将需要增加数据集,以精确地确定真实世界的环境响应。MATLAB 是一种解释型仿真器,可能无法为这些较大的、CPU 强度较高的定点仿真提供必需的性能。因此,开发者常常转向 C/C++。

加速定点仿真

AccelDSP Synthesis 综合工具的 M2C-Accelerator 自动生成一个硬件精确的定点 C++ 模型和测试基准,以加快定点仿真。

消除手动记录步骤节省了开发时间,大程度地减小了误差的引入。由于 C++ 是编译式的,因此可提供高达 1000 倍的仿真性能优势(图 6)。这种性能水平通常是那些要求理解定点数据作用的大型矢量集所必需的。

如果您想继续使用 MATLAB 可视化环境,包括其绘图功能,M2C-Accelerator 还可生成一个可用于原 MATLAB 测试基准脚本文件仿真的定点 C/C++ dll。

当您已经获得初始定点结果时,分析和细化改进的过程就可以开始了。AccelDSP Synthesis 综合工具提供了一组图形工具,包括表格化报告、变量探查和绘图等,以便在这一过程中提供辅助。

观测定点位增长

一个设计必须从整体上考虑,以有效地将浮点算法转换为定点模型。

如果从早期开始就一直未对数据路径进行检查,位增长可能会快速增长而产生过度的硬件,而过度约束位增长则可能造成无法接受的数值精度损失。获得对位增长进展情况较好观测性的一种通用技巧是向一个电子表格中输入变量。AccelDSP Synthesis 综合工具通过生成一个表格化、格式化的定点报告(图 7)而提供了此类级别的观测性。

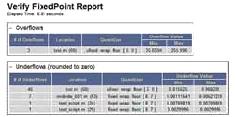

在优化硬件之前,您必须获得一个可以接受的定点响应。如果一个输出的信噪比 (SNR) 不在所需的技术规格之上,则必须对推断的量化值进行调整。这一过程通常由查找因变量上溢出和下溢出导致的重大误差开始。

上溢出和下溢出

关于输入数据动态范围的不良假设可能会引起由于变量的最高有效位 (MSB) 上溢出和最低有效位 (LSB) 下溢出而导致较大的定点误差的问题。您需要在观测和纠正更细微的定点误差之前先解决这些误差。

上溢出和下溢出报告,是 MATLAB 定点数据类型的固有属性,但不是 C/C++ 所固有的,且常常在模型重写过程中被省掉。但是,由 M2C-Accelerator 生成的 C++ 模型中包含了反映在仿真期间发生的所有上溢出和下溢出的量化例程。当这些情况发生时,它们将被汇总在"验证定点报告"中(图 8)。

一旦您解决了任何上溢出和下溢出问题,该定点模型的细化改进将更加依赖于可视化。如果另外的定点数据误差继续存在,那么您必须分析常量的作用。否则,您可以通过减小变量位宽来继续细化改进硬件的过程。在两种情况下,知道因某个特定变量的量化而引起的定点误差,在细化改进过程中都是一个有用的帮助。

图 7 – AccelDSP Synthesis 关于一个自适应滤波器的定点报告

图 8 – AccelDSP 验证定点报告

图 9 – Accel 关于一个变量的探查图

定点可视化

根据一组给定的数据集确定一个算法的合适定点响应,通常不是一种精确的科学行为。您常常不得不在数值精度方面做出一些折衷,以提高硬件效率。这一过程高度反复,且紧密耦合至绘图中所示定点效应的可视分析。但是,在一个输出信号上观测到不可接受的 SNR,并不总是表示那里错误地指定了一个量化值。对此,必须进行进一步的分析。

为了帮助进行这一过程,AccelDSP Synthesis 综合工具的 AccelProbe 工具以图形方式对一个给定仿真期间的任何变量的浮点和定点值进行了比较(图 9)。如果您使用的是 AccelProbe,您会迅速体会到特定变量的贡献使最终结果的误差累积的过程。您可以通过在 MATLAB 源码中增加语句 "accel_probe(variable_name)",来"探查"一个变量。

"定点历史"图可以让您感知一个变量在仿真期间可能遇到的频繁程度。如果一个值很少出现,则需要用以在动态范围内的高端或低端存储该值的附加硬件可能具有很小的值。

结论

当创建一个 DSP 算法的数学模型时,MATLAB 是天然之选,且出于硬件考虑,可以无阻碍地使用。将一个算法转换为在 FPGA 上实现的定点模型是一个复杂的、可从 AccelDSP Synthesis 综合工具提供的自动化、加速和可视化功能中大大受益的过程。

欲了解有关 AccelDSP Synthesis 综合工具的更多信息,请访问 www.xilinx.com/dsp。

作者:Tom Hill DSP 工具营销技术营销工程师 赛灵思公司 @xilinx.com">tom.hill@xilinx.com

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...