- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPU加法器的设计与实现

摘要:浮点运算器的核心运算部件是浮点加法器,它是实现浮点指令各种运算的基础,其设计优化对于提高浮点运算的速度和精度相当关键。文章从浮点加法器算法和电路实现的角度给出设计方法,通过VHDL语言在OuartusII中进行设计和验证,此加法器通过状态机控制运算,有效地降低了功耗,提高了速度,改善了性能。

关键词:浮点运算;加法器;设计;VHDL;状态机

在一般的处理器中,浮点加法、减法、转换和传送最终都是可以转换为采用浮点加法器实现,所以浮点加法器的使用频率高达55%,是使用频率最高的浮点运算模块。浮点加法的两个特点,一是它复杂,二是它被使用的频率在所有操作里面是最高的,所以它是现代微处理器和数字信号处理器中非常关键的部分。因此.浮点加法器的设计对FPU的整体性能十分重要。

1 运算方法

最基本的浮点加法算法需要相对最多的串行运算操作,它需要完成两个浮点操作数的求和运算,包括尾数部分的求和以及相应修改结果的指数值,而且最终结果必须是符合正IEEE754标准的规格化浮点数。

根据IEEE754浮点数表示方法与运算规则,其表示如公式(1)所示:

![]()

公式中:s为尾数的符号;t为指数的符号;e为尾数;f为指数。存储格式如图1所示。

为方便浮点数的乘除法运算,文中将e=1.n的表示方法改为e=1n,这样不断减少了进行乘除运算后的额外移位操作而且不增加加减法运算的运算量。

一般情况下,在浮点运算中为了提高数据表示的精度,通常需要将一段离散数据在实数轴上集中表示,这就需要对浮点数的表示方法进行限制,因此在浮点数中尾数的位数应大于指数的值,这样表示的优点是其数据精度相对较高。

本浮点加法模块,将采用突破浮点数表示方法的上述限制,使指数的值可以远远大于尾数的位数,这样数据的表达范围增大,实数轴上较宽的一段离散数据就可表达。然而这种做法的缺点是,一方面当数据表示宽度增大后,其精度就会降低,原因是表示的汇聚点距离拉大;另外一种情况是会出现数据移空现象,例如当一个操作数很大,而另一个操作数很小时,如果要进行减法运算,会出现在对阶移位的过程中将一个操作数移成了空数据,其值将会变成零。因此当两个操作数进行加法运算时,假如它们之间的差距很大,就可以不进行运算,直接将较大的操作数直接输出作为运算结果,就可将无谓操作避免,从而节省运行时间。

对于浮点数加法运算来说,它要求参与运算的两个操作数有一个共同的特点,那就是指数相同。只有当两个操作数的指数相同时才能够进行加法运算。浮点数加法如公式(2)所示:

![]()

签于浮点加法运算的特殊要求,两个浮点操作数存进行运算时需要通过以下几个步骤完成。第1步进行0操作数的检查,如果判定两个操作数中任意一个操作数为零,则没有必要进行后续一系列的操作,直接输出结果,从而节省运算时间;第2步,看它们的阶码是否相同,也就是小数点是否对齐,若相同则表示对齐,否则就必须通过对阶使小数点对齐,即阶码相同。第3步,对阶结束后,进行尾数求和,方法和定点加法运算相同。第4步,对结果进行规格化。第5步,进行必要的舍入处理。另外在进行加法器设计时,将和减法一起进行考虑,采用补码运算,这样将来的操作就可以直接调用加法核去完成。

2 加法器的设计实现

2.1 电路原理图

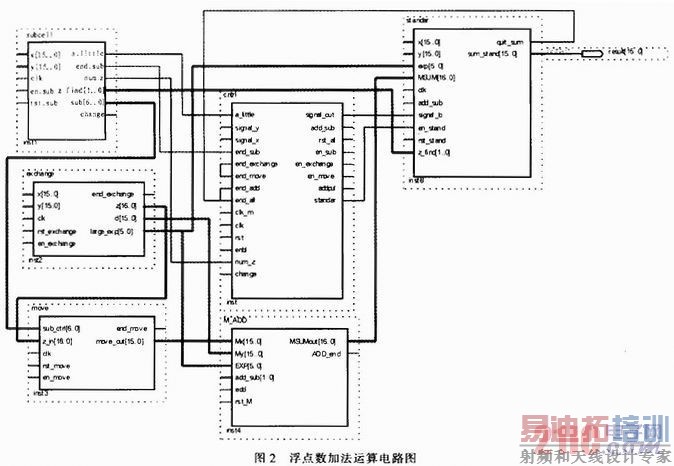

浮点加法运算模块电路原理如图2所示。主要由6个模块构成,分别是Subcell模块、exchange模块、move模块、M_add模块、standat模块、cntrl模块。下面将分别对这6个模块进行介绍。

1)Subcell模块

此模块的功能主要有以下4个方面:①0操作数的检查。将有关信息送到cntrl模块和standar模块,用于决定是否进行后续操作,以便节省运算的时间。②阶码大小的比较。将小数a_little传送到cntrl模块。③对阶。比较两个操作数的阶码,求出它们阶码的差值sub[6..0],送到move模块。④当这个模块运算结束或者有新操作数输入时,告知cntrl模块。

在图2中,当rst_sub=‘0’,此模块就正常工作;若rst_sub=‘1’,则所有的输出都是0。在零操作数检查的过程中,如果发现有0操作数的存在,则就令num_z<=‘1’;在此操作数的检查过程中还可以区分到底是哪一个操作数为零,假如操作数x为零,则就令z_find<=“0 1”;若是操作数y为零,则就令z_find<=“10”;若无0操作数,则z_find<=“00”。当对参与运算的两个操作数进行0操作数判别结束后,本模块在实现的过程中主要采用了5个条件语句来实现两个操作数大小的比较,通过比较可以算出阶码的差值。若两数的阶码相同,即小数点是对齐的,则进行位数的比较,当然这所有的比较都是通过不同的条件语句来实现的。所有的比较完毕,end_sub设为1。当有新的数据从x,y端输入的时候,根据程序的设置,相关进程会被唤醒,控制模块接收到进程发送来的脉冲change,就知道有新的操作数据输入,因此再次启动控制模块,进而进入另一个新的周期。

2)exchange模块

此模块的功能为:①向move模块输入小幂次浮点数尾数,②向M_ADD模块输入大幂次浮点数尾数。

此模块包含一个Process进程,当rst_exchange=‘0’并且en_exchange=‘1’,浮点数x,y的幂和尾数被拆开,存入不同变量。然后执行本模块所设置的4个条件语句,分别对两个浮点数进行处理,一方面将幂次小的操作数位数进行扩充,扩充为33位后传送到move模块中;另一方面将幂次大的操作数扩充成32为传送到M_ADD模块中。进程结束后,end_exchange置高电平,告知控制模块。

3)move模块

此模块的功能主要是为了实现两个操作数的对阶。在这个模块中设计了一个进程process(clk),它以clk为敏感信号,此进程还包含有2个条件语句模块。第1个模块主要是对变量进行更新。第2个模块主要是判断移位是否已经结束,并对相应的标志位进行设置。假如所移操作数的后8位是不为0的,那么在每个时钟的上升沿到来时继续进行向右的移动。

4)M_add模块

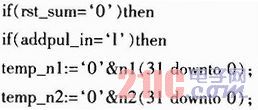

此模块的主要功能是对阶完成以后,对尾数进行运算。通过在每个尾数前加一位0来检测运算结果是否需要规格化。程序如下:

在进行加减法运算中分两种情况:当add_sub=“11”,执行Mx+My;当add_sub=“00”,执行Mx-My。具体由Cntrl模块的分析中给出。

5)standar模块

此模块的主要功能是对浮点运算的结果进行规格化处理。这个模块中有两个变量分别是ntemp和texp,该模块在首次执行时对它们进行初始化,否则只有当控制模块发出rst命令的时候才能对它们的初始值进行改变。当add_sub的值不同时,则将条件语句分成了不同的部分:

①当add_sub的取值为“00”或者当其取值为“01”的时候,可得M_ADD模块进行的是减法运算;如果运算结果是0,那么就直接将0输出;假如运算结果不为0,就需要对numb(15)进行考虑;假如其值是1的话,就不需要进行左移,直接执行语句:“sum_standar<=signal_b& temp_exp(5 downto0)&ntemp(14 downto 6);”。但是如果numb(15)的值是为0的,就需要进行左移。

②当add_sub=‘11’时,则M_ADD模块执行加法运算;如果numb(16)的值为1,就需要进行右移。而当numb(16)的值为0时,则不用进行规格化,直接输出。

6)cntrl模块

在这个模块中主要采用的是Mealy状态机,它和输入、输出、状态皆有关;一方面Mealy状态机要完成其状态的转化,需要等待本模块中CLK_m时钟信号的上升沿。另一方面如果subcell模块有了新的操作数的输入,本模块收到告知信号后,会将状态机重新运行。

在此对本设计模块中所使用状态机所包含的各个部分进行简要的阐述:

①说明部分

本部分主要是在ARCHITECTURE和BEGIN之间,用TYPE语句定义枚举型的数据类型(包含既定状态元素)status,状态变量xt_status和ct_ST atus定义为信号signal。主要用以下语句实现:

type status is(rst1,rst2,rst3,rst4,rst5,rst6,rst7);

signal xt_status,ct_status:status;

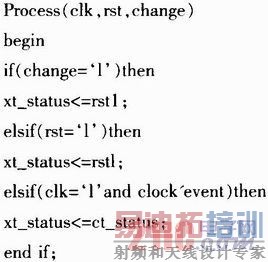

②主控时序进程

本部分主要以同步时序的方式工作,负责在时钟驱动下状态的转换进程。一般情况下,主控时序进程是不负责下一个具体状态的取值,只是简单机械地将代表次态ct_status信号中的内容送人现态信号xt_status。而ct_status信号的内容完全由其他进程根据实际情况来决定。当然此进程可以防止一些同步或异步的清零或者置位控制信号。在本部分中包含了敏感信号进程。

此进程的状态如下:

I Rst1:所有的信号进行初始化,准备跳至下一个状态。

ⅡRst2:启动subcell和exchange模块,跳至下一状态。

ⅢRst3:如果num_z=‘1’,也就是其中有一个操作数是零,就跳至状态Rst5,停止subcell和exchange两个模块。假如都不为零,则end_sub=‘1’和end_exchange=‘1’,开启move模块,转至Rst4状态。

ⅣRst4:停止move模块,开启M_ADD模块。

V Rst5:若有操作数为0,就直接开启standar模块,若无0,就等待M_ADD模块结束以后,再开启。开启后,M_ADD模块不可用。

ⅥRst6:standar模块运行结束以后,当clk_m=‘1’,关闭模块。当clk_m=‘0’,跳至Rst1。

ⅦRst7:这个状态称为不能够使用状态。

③主控组合进程

本部分的功能主要有两个方面,一方面是根据外部输入的控制信号和当前状态的状态值决定下一个状态的去向;另外一个方面是确定内外控制信号的内容。

④辅助进程

本模块的主要辅助进程为process(a_small,sign_x,sign_v,add_sub),这个进程的主要作用是能够对运算所产生结果的符号进行确定。

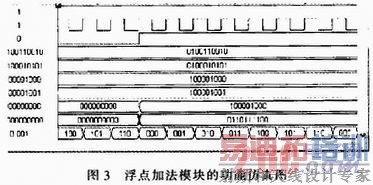

浮点加法运算模块的功能仿真如图3所示。

3 结束语

现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操作,在浮点运算中的浮点加法运算几乎占到全部运算操作的一半以上,因此,浮点加法器是现代信号处理系统中最重要的部件之一,它的设计与改进具有重要意义。

上一篇:高分辨率全帧CCD芯片FTF4027M的驱动电路设计

下一篇:PXI开放式的新技术于美国SEMICON

West正式发表