- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

伪码调相连续波雷达接收单元数字化研究

摘 要:为了缩短某类伪码调相正弦调频连续波雷达的探测时间,增加目标的自动识别功能,同时减少其接收单元的体积,用数字信号处理芯片代替了原来的模拟接收部分,并用一路卷积的算法代替了原来的多路相关。后期通过试验证明了此数字化接收系统的探测时间比原系统的接收时间缩短了50 ms,最高的目标识别率达到了75%,能满足实际应用的需求。

关键词:连续渡雷达;数字信号处理;自动识别;探测时间

0 引 言

伪码调相正弦调频连续波雷达是利用伪随机码良好的自相关特性进行测距,同时利用连续波雷达没有盲速盲相的优点进行动目标速度的测量。某一类伪码调相正弦调频雷达用一个中频信号去调制发射信号,对回波进行适当处理得到有距离灵敏度控制特性的目标多普勒信号。在此类雷达中接收单元的数字处理部分是在得到目标的多普勒信号以后,在高频、中频部分都是用模拟电路来实现的,为了提高接收单元的稳定性,减少接收单元的体积,缩短探测时间,同时实现目标的自动识别功能,需要开发出一种从视频回波直接进行数字化处理的接收单元来代替原接收单元,基于此目的,本文介绍一种数字化接收方案以及其硬件和软件设计。

l 数字化接收的原理

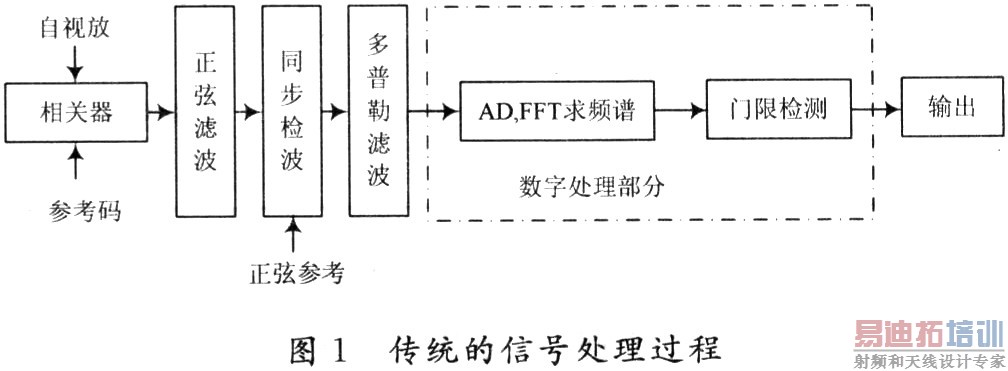

1.1 传统的信号处理过程

在此类雷达传统的信号处理过程中,视频回波先经过多路相关器的某个支路后得到对应距离单元的回波,然后经过正弦滤波后经同步检波得到具有距离灵敏度控制特性并且包含所需目标信息的多普勒信号,最后用数字处理的方法来判断此距离单元运动目标的速度等信息。当要对另外一个距离单元进行检测时只需要改变输入到相关器中伪码的延迟就可以对这个距离单元进行检测,在实际处理的过程中多个相关支路中所加入的伪码延迟时间是连续变化的,连续改变伪码的延迟就可以完成对所有距离单元的检测。在进行数字化接收设计以前某个距离支路的信号处理过程如图1所示,其他距离支路的处理过程与图1中所描述的完全一样。

1.2 数字化信号处理过程

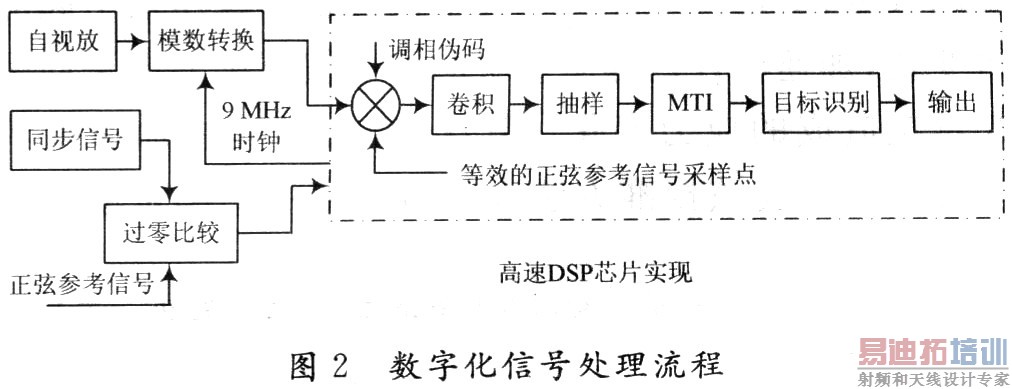

设计的数字化信号处理流程如图2所示。

信号处理过程如下:由DSP芯片产生的9 MHz时钟对视频回波进行采样,采集到的数字信号在DSP内乘上调相伪码和等效的参考信号采样点后进行卷积。用一次卷积代替多路相关,卷积输出经过抽样后得到各个距离单元的回波信号,然后对每个距离单元的回波进行MTI(动目标显示)检测,对有动目标的距离单元进行目标识别,然后进行输出提示。

2 硬件实施方案

2.1 主要芯片的选择

2.1.1 DSP芯片的选择

本系统在采集到信号以后所有的算法都是在DSP芯片内部完成的,因此运算量大,要达到实时处理,对DSP芯片的运算速度提出了较高的要求,且处理的数据量大,要求片内有较大存储空间。ADI公司的BLACKFIN系列中BF533的主频可以运行在600 MHz,内部存储数据的SRAM有68 KB,片外可以扩展到128 MB的SDRAM作为外部存储器,此外BF533还有以下三个优势可以提高运算速度:

(1)BF533内部有两个零开销的硬件循环机制,在一次程序执行完成以后可以省去执行条件是否成立的判断过程,直接执行若干次循环以后就执行下边的指令。

(2)BF533内部有两个乘法累加器,两个同时使用相当于在进行乘法运算时使主频达到了1 200 MHz,提高了指令执行速度。

(3)在BF533内部的L1存储区和内核运算单元之间的指令总线宽度是64 b,因此可以并发的同时执行一条32 b的指令和两条16 b的指令,提高了指令的执行速度。

综合考虑以上因素确定用ADI公司生产的BLACKFIN系列的BF533作为整个系统的DSP芯片。

2.1.2 模数转换器的选择

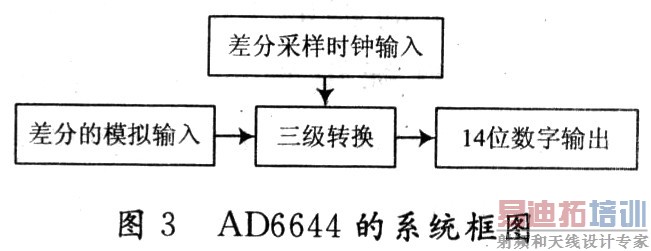

本系统设计的数字化接收单元中需要对视频放大器的输出直接进行采样,在视频放大器的输出信号中含有伪码成分,如果一个伪码周期中一个码元的宽度是0.33μs,则伪码的带宽在3 MHz左右,为了防止采到伪码的上升沿和下降沿决定用9 MHz的采样频率对视频回波进行采样,因为原信号处理中的A/D变换器是对多普勒信号进行采样,因此如果用原来的A/D变换器显然不能满足对模拟信号采样的采样定理。AD6644的最高采样频率可以达到65 MHz,并且它是一个高速、高性能、单片的14位模数转换器,采样时钟和模拟信号的差分输入方式可以在很大程度上对噪声进行抑制。同时AD6644采用的三级子区式转换结构,即保证了所需的转换精度和转换速度,又降低了功耗,也减小了模片尺寸。因此采用AD6644作为整个数字化接收单元中的模数变换器。图3给出了AD6644的系统框图。

2.2 输入及输出部分设计

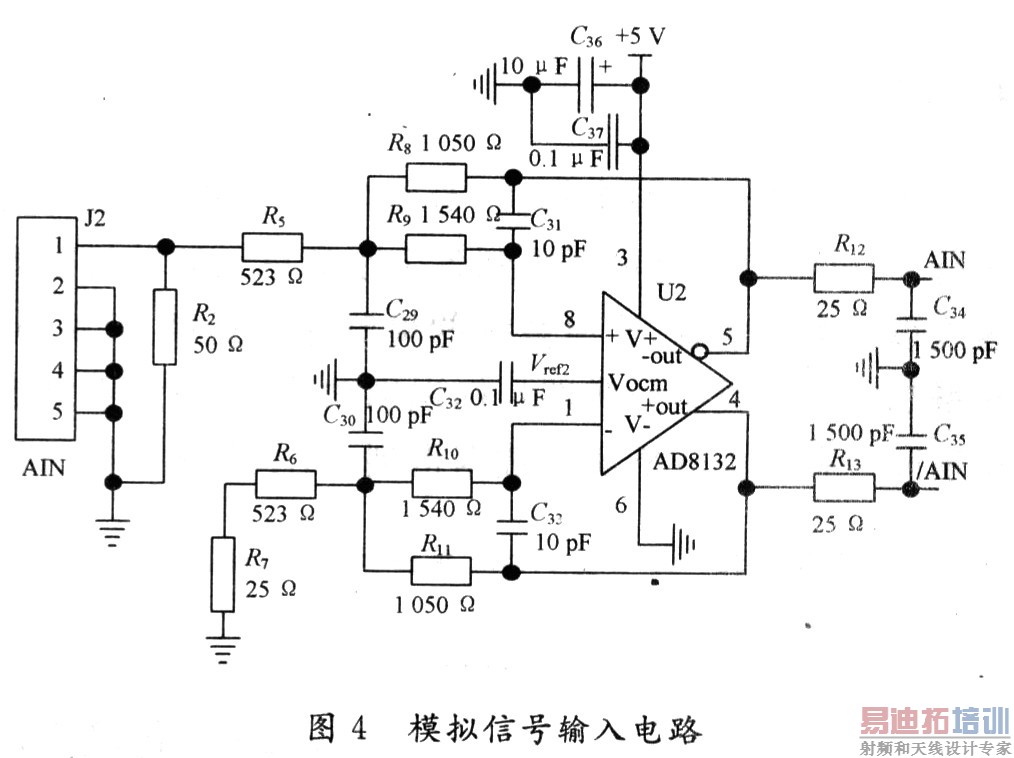

视频回波的输入电路主要完成两部分功能:单端输入转差分输入以抑制噪声,降低共模电压的影响;单端输入部分设计了一个带宽是4 MHz的二阶有源巴特沃思低通滤波器,保证信号的谱纯度同时抑制高频噪声。用AD公司的AD8132把单端输入转换成差分输入。实际应用时需要给AD8132的反相输入端加上与同相输入端完全对称的电路以保证电路工作的稳定性,同时为了更好地去除高频干扰,在差分的输出端用无源低通滤波进行了滤波,最后设计的模拟输入电路图如图4所示。

由于9 MHz的时钟信号不能由晶振直接产生,因此时钟信号由DSP芯片提供,时钟转差分输入由Mcl00EPT20D完成;AD6644_的数字输出信号,应尽量减小容性负载,同时为了保证数据输出端对总线的驱动能力,在输出端加了一个PHILIPS公司的74LVT245作为缓冲。为了保证过零比较的精度,提高抗干扰能力选择LM239D做为过零比较器。

3 软件设计

该数字化设计方案的所有数字处理过程都在DSP芯片内部实现,所以软件设计质量的高低直接决定了整个系统的处理性能。

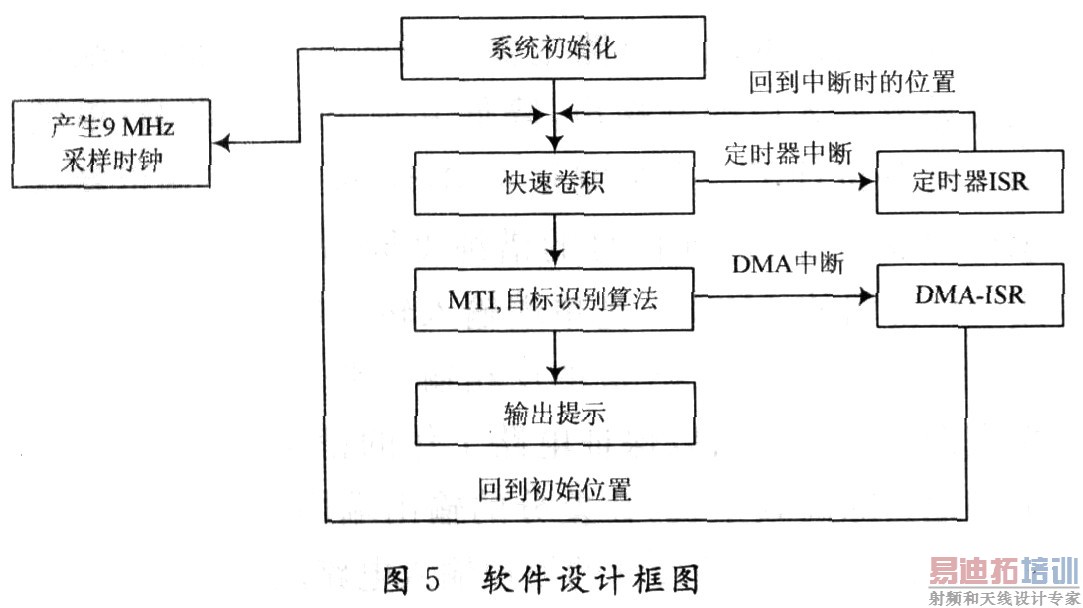

软件工作过程如下:加电以后系统先进行初始化,同时产生9 MHz的采样信号,然后启动DMA开始数据的传递。由于DMA在传输数据时不占用内部运算单元,因此在进行DMA传输的时候同时进行上一帧数据的卷积运算,计算完卷积后,对每个距离单元抽样得到的数据进行MTI,然后再进行目标识别的算法。由雷达的实际工作时序得到:在进行卷积计算时会发生定时器的中断,执行完定时器的ISR后回到卷积处继续执行;在MTI以及目标识别的算法运行时会产生DMA的中断,执行完DMA的ISR后回到卷积处重新依次执行,但是在执行完卷积运算后依然回到DMA中断发生时的位置进行运算。软件设计框图如图5所示。

4 结 语

用此系统运行整个算法,分析实验结果得到:开机运行640 ms以后就可以得到各个距离单元运动目标的速度以及类别信息,比原系统的检测速度提高30 9/6,同时增加了目标类型分辨即目标识别功能;让系统重复地识别同一种目标分析实验数据得到:对单人这一类目标的识别率达到了7O%,对单车的分辨率达到了75%,而对于多人的分辨率达到65%,多车的分辨率达到了60%。

综合以上实验数据可以肯定设计的硬件系统和软件算法在实际使用中是有效的,因此本系统具有一定的推广和使用价值。

上一篇:Fourier变换轮廓术中参数的选择和优化研究

下一篇:笔记本电脑声卡HD音效测试