- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FDATool的FIR滤波器设计方法(一)

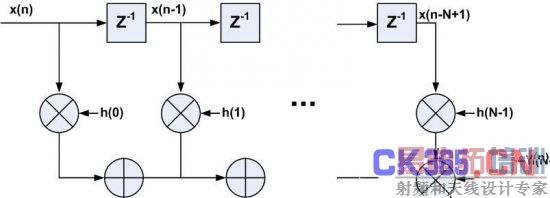

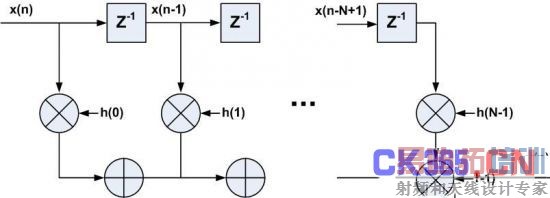

FIR滤波处理如下式所示,其中x(n)为输入信号,h(n)为FIR滤波系数,y(n)为经过滤波后的信号;N表示FIR滤波器的抽头数,滤波器阶数为N-1。

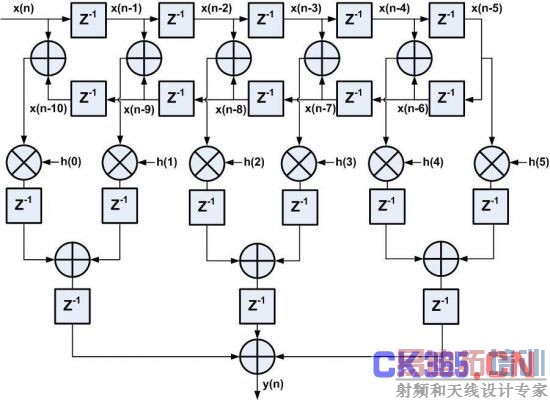

由上式可得到FIR滤波器在FPGA中的实现结构,如图1所示,主要由延迟单元Z-1、乘法器和累加器组成。此结构为直接型FIR滤波器结构,也称横向结构(transverse)。

图1

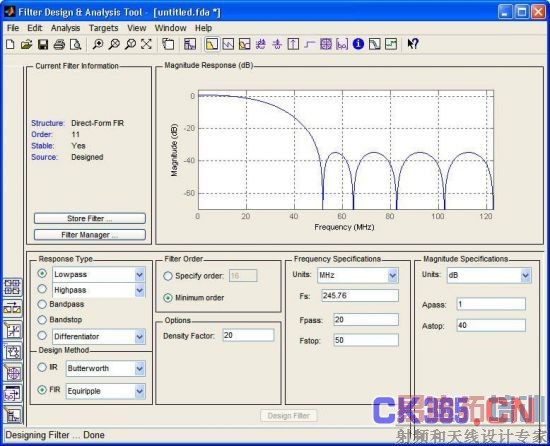

设计FIR滤波器的方法有多种,其中Matlab软件提供了很多关于滤波器设计的工具箱,FDATool就是一个很好的工具,如图2所示就是FDATool的界面,可以在Matlab的Command窗口中直接输入FDATool命令来调用。

图2

滤波器的设计首先需要设置的参数:

(1) Response Type:选择FIR滤波器的类型:低通、高通、带通和带阻等。如图3所示为Lowpass中的下拉选项,在DDC/DUC模块设计中,抽取和内插需要使用Halfband Lowpass类型,而channel filter需要使用Raised-cosine类型。

图3

(2) Design Method:FIR滤波器设计方法有多种,如图4所示,最常用的是窗函数设计法(Window)、等波纹设计法(Equiripple)和最小二乘法 (Least-Squares)等。其中窗函数设计法在学校课堂中是重点讲解的,提到FIR滤波器肯定会想到hamming、kaiser窗,但是实际应用中却很少使用,因为如果采用窗函数设计法,达到所期望的频率响应,与其它方法相比往往阶数会更多;而且窗函数设计法一般只参照通频带wp、抑制频带ws 和理想增益来设计滤波器,但是实际应用中通频带和抑制带的波纹也是需要考虑的,那在这种情况下,采用等波纹设计法就非常适用了。

图4

(3) Filter Order:设置滤波器的阶数,这个选项直接影响滤波器的性能,阶数越高,性能越好,但是相应在FPGA实现耗用的资源需要增多。在这个设置中提供2个选项:Specify order和MiNImum order,Specify order是工程师自己确定滤波器的阶数,Minimum order是让工具自动确定达到期望的频率相应所需要的最小阶数,因此具体选择哪个选项得视实际情况而定了。

图5

(4) Frequency Specification:设置频率响应的参数,包括采样频率Fs、通带频率Fpass和阻带频率Fstop。

图6

参数设置完成后,FDATool就会分析并且生成滤波系数,如图7所示,可以得到滤波器的频率相应曲线,并且可以通过File-》Export导出滤波系数,如图8所示。

图7

图8

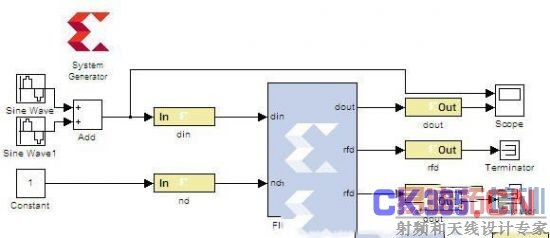

为了快速验证FIR滤波器的FPGA实现,使用Xilinx的System Generator工具,如图9所示为FIR滤波器的验证模型,其中通过Gateway In和Gateway out模块分隔matlab simulink模块和Xilinx FPGA模块,matlab simulink模块用于产生测试源,接收并显示滤波后波形。还有System Generator Token用于生成Xilinx FPGA模块的HDL代码。

图9

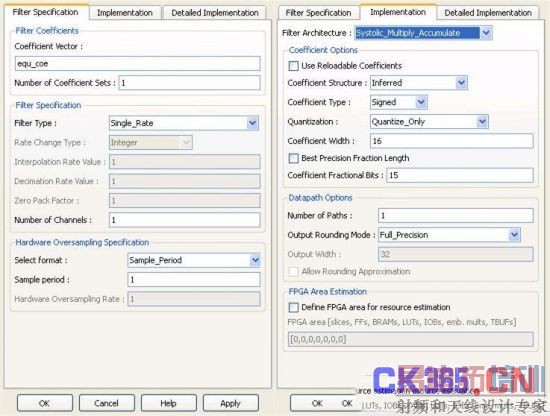

其中FIR Compiler 5.0模块的参数设置如图10所示,滤波系数直接调用FDATool生成的滤波系数equ_coe,输出为全精度数据。

图10

得到输出结果如图11所示,上边图为输入原波形,由两个频率分量的正弦波叠加而成,频率分别为2MHz和100MHz,经过FIR滤波之后,100MHz频率分量被滤除。

图11

FIR滤波器根据输入数据速率的不同可分为串行结构、半并行结构和全并行结构。串行结构的FIR滤波器是将并行数据串行输入,所需的DSP资源较少,但是数据吞吐率较低;而全并行结构的FIR滤波器数据是并行输入,滤波系数的个数就决定了所需DSP资源的个数,资源耗用较多,但是吞吐率可以做到很大。在大多数应用中,如无线数字中频处理,所需数据吞吐率一般都较高,因此采用的是全并行结构的FIR滤波器。

本文引用地址:http://www.eepw.com.cn/article/249651.htm

全并行FIR滤波器根据实现结构不同可分为:直接型(Transverse)、转置型(Transpose)和脉动型(Systolic),这一节主要讲解直接型FIR滤波器设计。

(一)直接型

直接型FIR滤波器在上一节中也有介绍,如图1所示,数据x(n)移入并寄存,如果有11个抽头,因此直接型FIR滤波器需要11个乘加模块。

图1

FPGA实现时,直接采用上图中结构,不对中间数据寄存,则关键路径是x(n)h(0)+x(n-1)h(1)…x(n-N+1)h(N-1),以阶数10的FIR滤波器为例,如下为抽头系数:

coe_0 = -1241

coe_1 = -650

coe_2 = 1300

coe_3 = 4739

coe_4 = 8126

coe_5 = 9544

coe_6 = 8126

coe_7 = 4739

coe_8 = 1300

coe_9 = -650

coe_10 = -1241

数据输入时打了一拍,输出时打了一拍。综合后结果如下:

Number of Slice Registers: 2

Number of Slice LUTs: 19

Number of DSP48E1s: 11

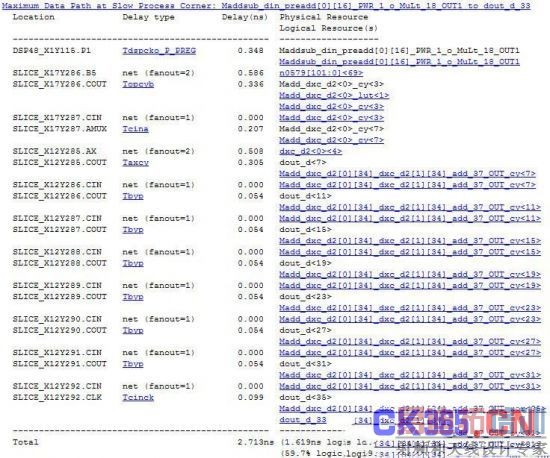

关键路径中数据路径延时报告如图2所示,数据路径延时包括乘法器延时Tdspcko PCOUT AREG MULT (3.001ns)+ 10个级联加法器延时Tdspdo PCIN PCOUT(1.219),数据路径延时总共15.017ns,因此fmax最大不过66.273MHz。可以发现综合器自动将乘法器和加法器在 DSP48E1中实现。

图2

加法树实现:

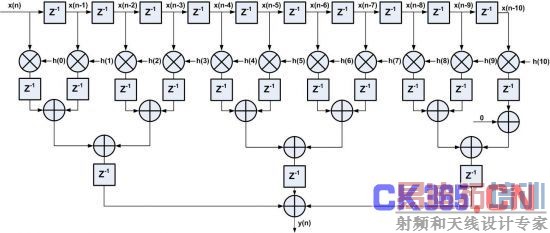

直接型FIR滤波器的一般实现方法关键路径中有较多级的加法器,所有加法器延时累加后导致关键路径延时较大,对整个FIR滤波器的性能造成了很大影响。为了解决加法器延时累加的问题,可采用加法树结构,如图3所示为采用了加法数的直接型FIR滤波器结构,这种层次化的树型结构,使加法器逻辑由级联结构转化成并行结构,这样整个路径的延时减小。

图3

流水线实现:

虽然直接型FIR滤波器采用加法树结构后优化了关键路径,但是时序还是不够理想,因为关键路径上至少有一个乘法器和一个加法器的延时,如果想竟可能的优化时序,可以分隔乘法器和加法器逻辑,中间加一级寄存器,即采用流水线实现。

那如何有效地分割逻辑呢 可以在图3中加法树结构的基础上分割,在原先的关键路径上,乘法器延时3.001ns,加法器延时1.219ns,因此可以将逻辑分割成如下**:

第1级:乘法器

第2级:2级加法器

第3级:3个数累加即2级加法器

如图4所示为流水线实现的FIR滤波器,逻辑分割后的关键路径是乘法器那一级,理论分析得到的延时只有3.001ns,如果时钟约束到250MHz可满足时序要求。

图4

实际得到综合结果如下:

Number of Slice Registers: 105

Number of Slice LUTs: 124

Number of DSP48E1s: 11

Minimum period: 3.037ns{1} (Maximum frequency: 329.272MHz)

fmax能达到329.272MHz,延时基本与预期的差不多,FIR滤波器能达到这样的性能基本能满足大多数应用了。

线性相位FIR滤波器:

FIR滤波器有一特征:线性相位,直接表现在抽头系数上,抽头系数为偶对称或者奇对称,在这节实例中,系数是偶对称的,即 h(0)=h(10),h(1)=h(9),h(2)=h(8),h(3)=h(7),h(4)=h(6),直接型FIR结构优化后如图5所示,输入数据在与系数相乘之前,因系数对称,可以先将相同系数对应的数据进行预加操作,然后再与系数相乘,如此做法的好处是是乘法器资源减少了近一半,此例中DSP资源由原先需要11个到现在只需6个。而且,在Xilinx FPGA中的DSP48E1资源专门为线性相位FIR滤波器应用提供了预加pre-adder结构,即预加和乘法都可以在1个DSP48E1中完成,这样大大缩短了数据路径的延时,有利于时序收敛。

图5

实际得到综合结果如下:

Number of Slice Registers: 184

Number of Slice LUTs: 173

Number of DSP48E1s: 6

Minimum period: 2.854ns{1} (Maximum frequency: 350.385MHz)

fmax能达到350.385MHz,由于采用了加法树结构,避免了加法器级联延时,并且分了3级流水线实现。关键路径数据延时报告如图6所示,路径是从 DSP48E1输出端到dout_d,但是光从代码中看DSP48E1端到dout_d中间应该还有一级加法器的寄存,原来这个加法器采用了 DSP48E1中的累加器实现了。

图6

上一篇:一种基于HMC5843和Zigbee的三维姿态监测系统设计

下一篇:基于CPLD的PC104系统与CAN总线网络通信设计