- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

无载频脉冲探地雷达主控系统小型化设计

无载频脉冲探地雷达是宽带穿透雷达的一种,它利用电磁脉冲地下传播时,在介质交界面或地下目标处发生反射的性质进行地下浅层探测。它的组成包括宽带收发天线,电磁脉冲发射机,取样保持接收机,主控系统,计算机。从自动化控制的角度而言,主控系统处于中心地位。主控系统通过屏蔽性能良好的多芯同轴线电缆与一体化安装的发射机接收机连接,完全控制电磁脉冲的激发和回波的取样。主控系统使用通用接口与计算机数据通信,接收参数设置字,上传采集数据。

现有的无载频脉冲探地雷达主控系统大多以众多分立的中小规模集成元件搭建控制功能,存在系统功能无法升级,整板功耗较大,电路焊点和元件间走线数目多的特点,其电路板调试工作量大,日后维护中出现故障不易定位。本文针对主控系统功能需求和特点,以硬件划分的思想,研制了一种新型的主控系统,解决了上述问题。

1. 主控系统功能需求和特点

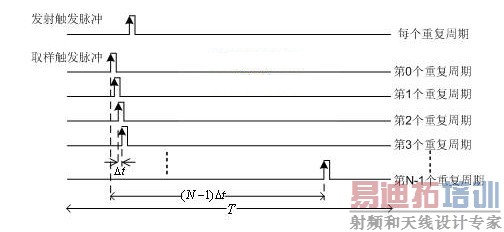

主控系统需要产生两路同步的触发脉冲。一路是重复周期为 T(微秒量级)的发射触发脉冲,它用来激发发射机窄电磁脉冲发射源;另一路是取样触发脉冲,它重复周期亦为 ,但第i +1( )个重复周期里,触发时刻相对第 个重复周期触发时刻延后 (一般十几皮秒到纳秒量级),它用来周期的开启接收机取样门,完成等效时间取样,如图1所示。从而对接收到的准周期重复的回波的取样时窗为 ,接收机输出信号相对该取样时窗信号,时域展宽比为 ,称为一道回波,显然其频带转换到了音频范围,所以等效时间取样降低了模数转换的成本。

回波信号特点是,最先接收的收发天线间直达波幅度最大,地下介质属损耗媒质,同样的反射系数下,深处目标反射信号比浅处目标反射信号弱。为了更好的关注目标深度信息,要对每道回波进行随接收时间增益增大的放大,称为时变增益放大。

每道回波经时变增益放大处理后就可以数字化了。若采用16位分辨率的ADC采样,在脉冲重复频率为200kHz时,数据采集速率是3.2Mbps,用USB作为同计算机的接口,既充分满足了数据传送速率要求,又方便了与计算机的连接。

FPGA非常适合实现硬件级的状态流程控制逻辑,产生具有同步时序关系的并行控制信号,并集成实现逻辑接口,所以可用其作为主控芯片实现专用的逻辑功能。

图1 发射机接收机触发控制示意图

2. 主控系统的硬件设计

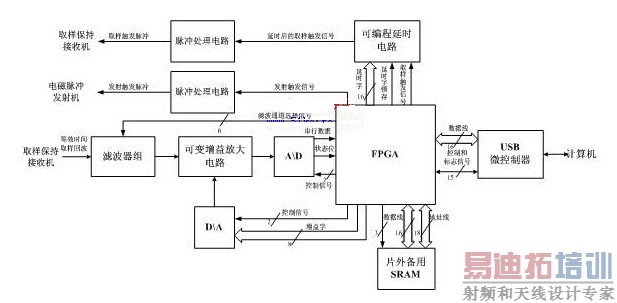

本主控系统中,单片FPGA产生各个所需的同步时序数字信号,控制模拟电路模块:等效时间取样与触发信号生成模块,时变增益放大模块,模拟滤波器组模块,ADC模块,并以主方式访问USB微控制器。

主控系统硬件设计框图如图2所示。

图2 主控系统硬件框图

选用XILINX公司XC3S400-PQ208型号FPGA作为主控芯片。它具有141个可编程用户管脚,主控芯片需要近120个左右管脚;具有7168个四输入查找表(LUT)和触发器(FF)等可编程逻辑资源,16块1024*18位的双口Block RAM等其他硬件资源[1],可满足主控功能实现需求,且性价比较高。

2.1 触发脉冲生成电路设计

触发脉冲生成电路包括可编程延时电路和两个脉冲处理电路。可编程延时电路用两级级连的八位可编程延时延迟线DS1023设计,它功能上代替了快斜波和慢斜波进行比较实现步进延时的分立电路[2]。DS1023具有0.25ns,0.5ns,1ns,2ns,5ns五种延时步长类型,接口为5V CMOS电平,兼容5V TTL输入信号标准,故能和XC3s400实现无缝互连。把两级DS1023级连,XC3s400产生的取样触发信号经过一块延时步长0.25ns的DS1023-25输出后,作为延时步长5ns的DS1023-500的输入,可以设计出最大时窗为1279.75ns,最小步长为0.25ns的可编程延时电路。

XC3s400用户管脚在3.3V的LVTTL信号标准下,输出信号高电平最大只能接近3.3V,最大驱动电流24mA;DS1023延时信号输出管脚输出高电平不到5V,最大驱动电流1mA。考虑到发射机接收机内脉冲触发电路等效输入负载,以及长电缆表现容性对脉冲衰减和畸变,两者都无法直接作为触发脉冲。用可工作于 12V的TI公司宽带脉冲运放THS3001设计正相放大器,将两路触发信号高电平增至9V左右,经实验测量,可在发射机接收机触发脉冲输入端得到良好的TTL电平触发脉冲。

2.2 回波数据采集通道设计

发射机和接收机可以选择不同中心频率天线,等效时间取样步长亦可由FPGA改变延时字更新方式来改变,故接收机输出的等效时间取样回波中心频率不同。例如,对于900MHz中心频率收发天线,100kHz脉冲重复频率,取样步长0.25ns时,等效时间取样回波中心频率为22.5kHz。本设计选用集成滤波器MAX274设计八阶低通和带通滤波器,同双路双控模拟开关ADG621构成可程控选择滤波通道的模拟滤波器组,由XC3S400通过高低电平信号通断模拟开关,选通某个合适的滤波器通道关闭其他滤波器通道进行滤波。

可变增益放大电路由两级低噪可变增益放大器AD603级连实现。一个3.3V的硅稳压管电压经两组独立可调串连电阻分压结构后提供两个电压基准分别至两级AD603 NPOS管脚;对电压型DAC AD7305输出模拟电压,分压后提供可变电压至两级AD603 VPOS管脚。两级AD603在DAC转换电压控制下,增益动态范围可以达到80dB。AD7305的数模转换建立时间不高于2 ,小于探地雷达的脉冲重复周期,故能使得XC3S400按照脉冲重复频率向AD7305锁存时变增益曲线表数据。

ADC模块选用可工作于从模式的16位ADC AD7677。因为等效时间取样回波信号的获取与取样触发信号同步,所以ADC从模式受控于XC3S400便利了数据采集和存储。通过设置其EXT管脚为高电平,WARP和IMPULSE管脚为低电平,可令其数模转换受控于数模转换信号 。

2.3 USB2.0微控制器与FPGA的接口设计

USB2.0微控制器选用Cypress公司FX2LP系列CY7C68013A芯片,它功能上兼容FX2系列的CY7C68013。它具有实现了USB协议栈的设备端接口和微控制器8051,能自动完成USB事务处理,故无需FPGA响应处理USB事务,减轻了本系统逻辑设计的复杂度。CY7C68013A作为从设备时,其接口模式为slave FIFO,CY7C68013A把片上总量为4KB的量子FIFO作为USB串行接口引擎(SIE)与外部设备交换数据的缓存。slave FIFO接口异步读写最高133Mbps,读写时序产生方式灵活,FPGA可把CY7C68013A视为四个端点(EP2,EP4,EP6,EP8)异步FIFO,直接进行16位数据读写,无需8051干预。本设计选用56个管脚的CY7C68013A,相比更多管脚的型号,它只保留了可配置成slave FIFO接口的A,B,D端口。

3. 主控系统的固件开发

3.1 XC3S400固件开发

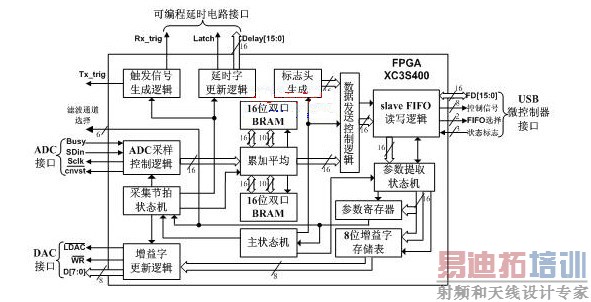

FPGA内部实现逻辑功能模块结构以及外部主要接口信号如图3所示。

图3 FPGA逻辑设计和主要接口信号框图

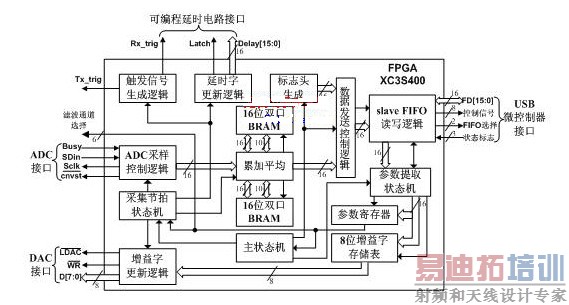

各逻辑模块是以外部有源晶振50MHz时钟为基准的同步时序逻辑。根据参数寄存器设置,主状态机可选通使能标志头生成逻辑,参数提取状态机,采集节拍状态机,数据发送控制逻辑,完成参数接收,数据采集,累加平均,数据发送等流程。各逻辑模块间构成树型控制结构,如图4所示。该设计用Verilog语言描述[3],在Xilinx公司ISE7.1i开发环境下前后仿真,约束综合,实现得到编程文件。使用Chipscope pro7.1i在线调试FPGA,检查被设置为触发的待检内部信号的逻辑转换全程,能较为快速地发现设计问题,进而修改设计文件或约束文件。

图4 FPGA内部逻辑模块的树状控制结构图

3.2 CY7C68013A程序设计

本USB应用需要IN,OUT端点各一个,把端点2配置为OUT端点,端点6配置为IN端点,两个端点FIFO均配置为4重缓冲,充分利用了8块512字节的“量子FIFO”缓存。CY7C68013A固件开发使用Cypress公司提供的通用固件程序框架,只须在相应流程的函数体中添加入用户代码[4][5]。其工作于从模式,系统空闲时反复循环调用的TD_Poll()函数体中不添加任何用户任务代码,只需修改8051复位后初始化函数TD_INIt()函数体,完成CPU配置,接口配置,端点6和端点2,及其FIFO配置等寄存器的设置。为了避免CY7C68013A主频时钟可能对电路板其他信号产生EMI干扰,把CPU配置寄存器位CLKOE设置为0,将CLKOUT引脚悬空,不输出内部48MHz主频时钟。

在主控系统固件开发中,为了保证主控系统上电后XC3S400和CY7C68013A之间不会因配置加载完成时间先后不同而引起不可预料的逻辑问题,在FPGA逻辑中设置一个初始化计数器,当它从配置芯片XCF02S加载后,只有该计数器计数,待等待时间(如1秒)过后,计数器溢出,令一个使能信号置位,使能所有逻辑块。这就能充分保证FPGA实施主控时CY7C68013A已从EEPROM加载程序,并完成了寄存器初始化。

4. 结论

<