- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

实现软件GPS的软硬件设计讨论(Ⅱ)

GPS接收机模拟前端架构

在以MAX2741/MAX2741A为代表的GPS接收机架构中,MAX2741是专门为利用宿主机的处理能力完成GPS功能的应用设计的模拟前端。可以预期,类似架构的GPS接收机逐渐会因其低总体成本成为市场主流。其架构为一个两次下变频超外差接收机,输出为数字化的第二中频信号流。除了射频输入滤波器、一中频输出滤波器和锁相环环路滤波器需要在片外搭建,MAX2741片内集成了包括本振谐振槽路在内的所有组成完整接收机需要的其他元件。

MAX2471只在二中频滤波量化、参考频率配置方面支持灵活配置,通道中二中频以上和本振部分相对固定;对于这样一个接收机,参考频率的分频和上述3个滤波器的设计在系统设计规划阶段可以根据面向C/A码调制带宽确定,一般不再需要调整。

二中频带宽、输出直流消除和增益可以在接收过程中自适应优化。

直流对消主要是面向接收机二中频变频器偏置漂移和相位漂移,形成低频阻带;可以通过统计样本集中零两侧的点数平衡予以调节。

增益通过量化台阶的位置影响接收效果;引用继承的设置或根据输出数据的统计分布快速建立初步设置后,需要在工作中自适应。后面段落另有针对初步设置的讨论。

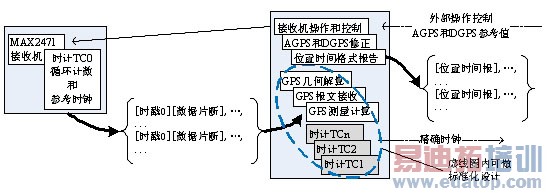

参考图4,通过为MAX2741提供一个虚拟的底层时计可以改善软件GPS系统设计对宿主硬件的依赖性。虚拟时计可由宿主机处理器的内嵌硬件实现的(如常见的捕获时间计数器),也可由单独的硬件实现。输出的串行数据本身是时序串行的,已经带有时间信息。虚拟时计记录在没有串行数据期间的时间。

虚拟时计使接收机接口标准化,同时明确了接收机与处理接口的实时性要求。以虚拟时计和串行流数据流为接口,硬件接口和软件移植被简化为这个接口的实现。

基于片段生成的样本集和部分滑动相关算法

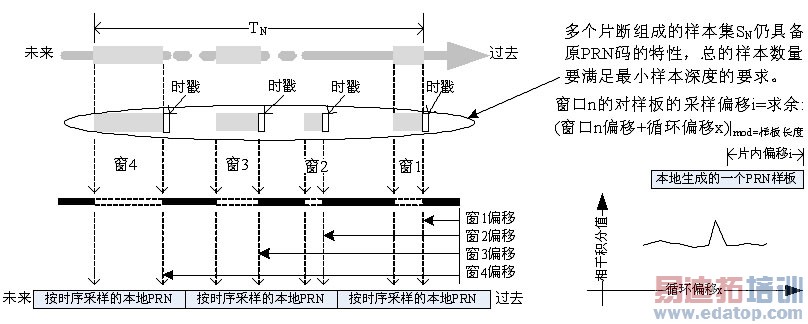

参考第一部分的讨论,保证有效的相关计算需要在时间跨度<20ms之内采集到至少包括总量超过折合1ms连续数据量的一个样本集。并不是针对GPS应用设计的宿主系统不一定能保证连续的数据采集和缓冲;因此,从通用性出发,需要考虑利用图4中带时戳数据片断拼制一个用于相关计算的集。

图4:增加一个虚拟时计br>图6:频偏扫描和错相扫描的积和频相平面的分布。

第一部分已提到伪随机序列的片断,如果保持足够的样本数、仍保持原序列的特性;参考5示意,由片断组成的序列作相关计算时如果之间的间隔较短,可以用0值(或0和1交替序列)充填连接成更长序列;但较长的序列需要投入更大的计算开销。是充填还是分别处理与采用的算法有关;采用FFT时适合充填,滑移相关时适合分开。

针对一个特定的PRN码,接收到的序列中是否存在同样的码以及这个码在序列中所在的位置都由相关积反映;如图5右下方的示意,当采用不同的偏移使本地产生的PRN码片滑动时,如果接收序列中存在该PRN码、在本地码片滑动到与接收序列中该码一致的位置时相关积出现峰值(或者谷值)。

改善GPS设计的硬件无关性。

图5:针对多个片断进行的相干计算的示意。

本地生成相干码片的过程把一个本地生成PRN码序按接收序列的时钟序列采样;此时钟由接收机的采样时钟确定,与接收序列中带有的GPS系统时钟没有直接关系;生成本地PRN序列所采用的时钟(包括生成本地载波所采用的时钟)则是要做到与GPS系统一致的时钟、即需要测量的时钟。

GPS接收所要求的信噪比不能保证有效的载波恢复和同步,需要先利用PRN的时域相关抑制非相干部分才能有效地识别出载波。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:优化DBDM手机处理器之间的通信

下一篇:设计基于伽利略卫星网络的GPS系统