PLL环路滤波求助

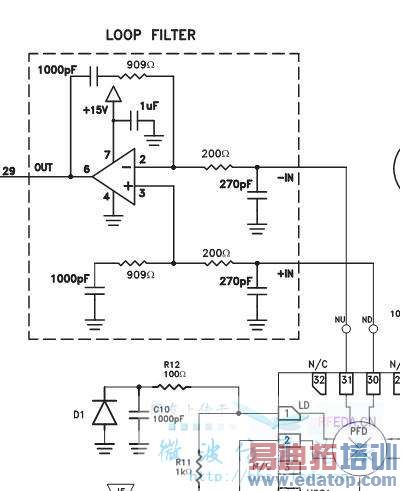

这是hittite一款pll datasheet里面的环路滤波电路,是差分有源低通滤波电路,我对模拟电路不太熟,我认为这个电路对直流的放大理论上为无穷大啊,都是限幅,输出没法对vco进行调节,我实测出来也是这样,都是14v左右,希望高手解释一下。其他论坛我不熟悉,所以就发到这里了,麻烦大家了。

个人认为第三脚的电压应该调节到电源电压的一半左右。图中电路图1000pF电容和电阻909R不应该是串联的关系,应该是并联到地。你可以尝试调节一下。

感谢楼上的朋友,我去试一下。我在书上找到一段话,“有源滤波器的直流增益趋于无穷(实际器件增益一千多),说明当采用有源比例积分滤波器时,为支撑控制电压Ve所需相位误差Theta趋近于零”,理解不了。

这是一个典型的环路积分滤波电路,这个电路应该是对的(当然具体电阻电容参数要看工作频率范围)。积分频响理论上对DC的放大就是无穷大的。这个(积分)环路滤波电路对所在锁相环的电路的好处就是减少相位移的跟踪误差。具体道理可以参考常用的锁相环电路书籍资料或自行推导。

运放的输出(6脚)DC电压应该在接近0或15V,如果不放心这样的DC电压损坏运放或其负载可以加二极管箝位防止电压过高(底)。如果确定不会损坏或负载电路已经有类似保护电路就不需加了。

电路没能跳出可能是因为电路没有锁住或其他原因。

“积分频响理论上对DC的放大就是无穷大的。”“运放的输出(6脚)DC电压应该在接近0或15V”如果是这样,直流输出电压固定,那VCO输出频率不也就只能共作在0V和15V对应的频率上了啊,那还怎么锁相啊?不解啊。

直流是指没有非直流信号情况下的(如VCO关闭或锁相环到积分滤波器输入开路等),当锁相环闭路时,如果最后锁住,那么电路在刚开始运算放大器的输出(6脚)先在接近15V和0V之间震荡,然后该震荡的幅度组建减小,到一定程度后就锁住。当然这个过程可能很短(估计几个到几十个回合)。如果锁不住我估计那么要么用永远在接近15V或0V,要么输出地是类似随机的波形。

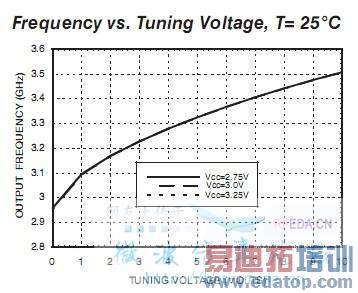

具体点说吧,这是我要用于PLL环路中VCO频率和控制电压的关系曲线,我想让PLL输出在3.3G,对应也就是运放的输出控制电压要差不多4.5V,运放用OP27(放大系数A差不多1500),那锁住时PFD的输出电压是不是就是4.5V/1500=3mV,是不是这个意思?如果考虑理想的运放器件放大系数A趋于无穷,那PFD的输出是不是就趋于零?

觉得应该是这样的。

这样的话总觉得有点不对,如果运放的放大倍数很大,那PFD的输出电压不是一直都必须很小啊。

上一篇:插入介质波导的一种新型馈电结构

下一篇:射频滤波设计中问题请教