新手求助Hspice仿真问题

录入:edatop.com 阅读:

把出错行注释掉,下一行继续报错,求各位帮助,是我生成的spf网表有问题?还是最开始的数字电路就有问题?

能否告知如何更改?

error信息看的不全

- ****** HSPICE -- J-2014.09-SP2 64-BIT (Feb 26 2015) RHEL64 ******

- Copyright (C) 2014 Synopsys, Inc. All Rights Reserved.

- Unpublished-rights reserved under US copyright laws.

- This program is protected by law and is subject to the

- terms and conditions of the license agreement from Synopsys.

- Use of this program is your acceptance to be bound by the

- license agreement. HSPICE is the trademark of Synopsys, Inc.

- Input File: s38417_trojan1.spf

- Command line options: s38417_trojan1.spf

- lic:

- lic:

- lic:

- lic:

- lic:

- lic:

- lic:

- lic:

- lic:

- lic:

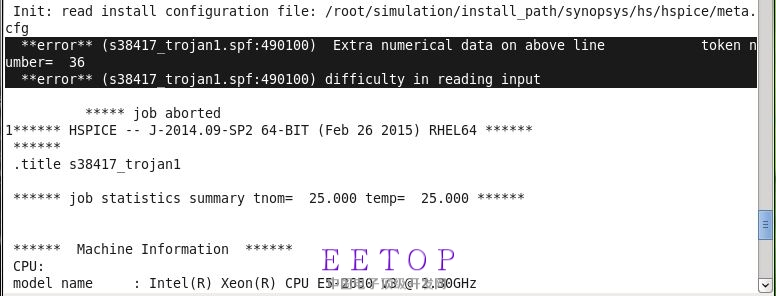

- Init: read install configuration file: /root/simulation/install_path/synopsys/hs/hspice/meta.cfg

- **error** (s38417_trojan1.spf:490100) Extra numerical data on above line token number= 36

- **error** (s38417_trojan1.spf:490100) difficulty in reading input

- ***** job aborted

- 1****** HSPICE -- J-2014.09-SP2 64-BIT (Feb 26 2015) RHEL64 ******

- ******

- .title s38417_trojan1

- ****** job statistics summary tnom= 25.000 temp= 25.000 ******

-

-

- ****** Machine Information ******

- CPU:

- model name : Intel(R) Xeon(R) CPU E5-2650 v3 @ 2.30GHz

- cpu MHz : 2301.000

-

- OS:

- Linux version 2.6.32-573.22.1.el6.x86_64 (mockbuild@c6b8.bsys.dev.centos.org) (gcc version 4.4.7 20120313 (Red Hat 4.4.7-16) (GCC) ) #1 SMP Wed Mar 23 03:35:39 UTC 2016

- ****** HSPICE Threads Information ******

- Command Line Threads Count : 1

- Available CPU Count : 40

- Actual Threads Count : 1

- ****** Circuit Statistics ******

- # nodes = 0 # elements = 296622

- # resistors = 180603 # capacitors = 116019 # inductors = 0

- # mutual_inds = 0 # vccs = 0 # vcvs = 0

- # cccs = 0 # ccvs = 0 # volt_srcs = 0

- # curr_srcs = 0 # diodes = 0 # bjts = 0

- # jfets = 0 # mosfets = 0 # U elements = 0

- # T elements = 0 # W elements = 0 # B elements = 0

- # S elements = 0 # P elements = 0 # va device = 0

- # vector_srcs = 0 # N elements = 0

- ****** Runtime Statistics (seconds) ******

- analysis time # points tot. iter conv.iter

- op point 0.00 1 0

- readin 10.38

- errchk 0.00

- setup 0.00

- output 0.00

- peak memory used 1294.95 megabytes

- total cpu time 10.78 seconds

- total elapsed time 11.65 seconds

- job started at 15:27:51 04/18/2016

- job ended at 15:28:03 04/18/2016

- >error ***** hspice job aborted

- lic: Release hspice token(s)

- lic: total license checkout elapse time: 0.38(s)

全部的log信息,还需要看spf文件吗?

给大家说一下我面临的难题。

毕设,我修改了一个verilog标准电路,综合得到的verilog网表,老师想看到修改过的电路电源电压的波形和原标准电路电源电压波形有无差别,就让我用Hspice仿真。

师兄让我用IC Compiler把verilog网表输出为def文件,再用StarRC抽取为spef网表,自己加入数字激励,进行Hspice仿真。

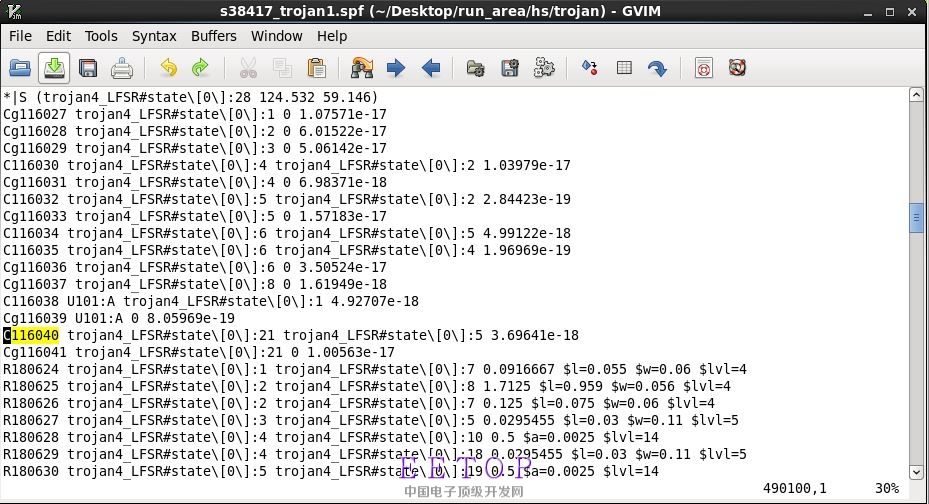

我感觉是我的spef网表有问题,因为StarRC抽取的只是寄生参数网表。

逻辑结构被忽略,是否成为了我对spef网表进行仿真时频频报错的原因?

希望有好心的大神帮帮我这个菜鸟本科生,解答一下让我知道问题出在哪,我做了将近一个星期这个仿真结果还是没出来,卡得我太难受了。

这个网表是有问题的 :在hspice里面是有意义的 不能代表端口

问题解决了,网表有问题,starRC抽取的spf文件里面好多节点标号都出现了\[0\] \[1\] \[...\]这样的格式,把它修改为[0]就可以了

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:关于混频器线性度仿真的取值问题

下一篇:cadence5141昨晚跑了一晚,今天一直提示 insufficient disk