急~~ADC中S/H(采样保持)电路的问题

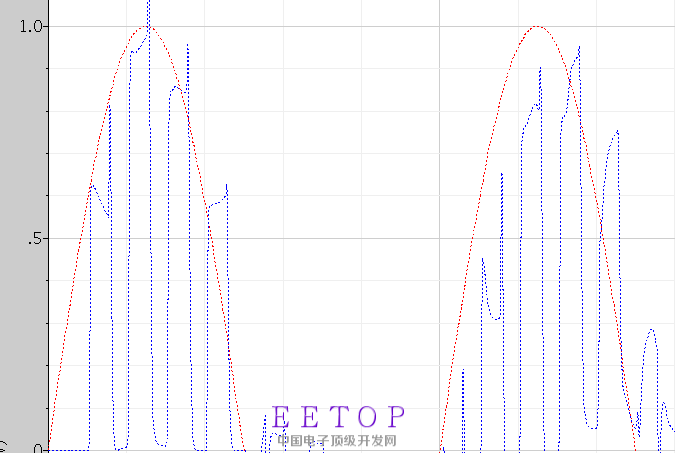

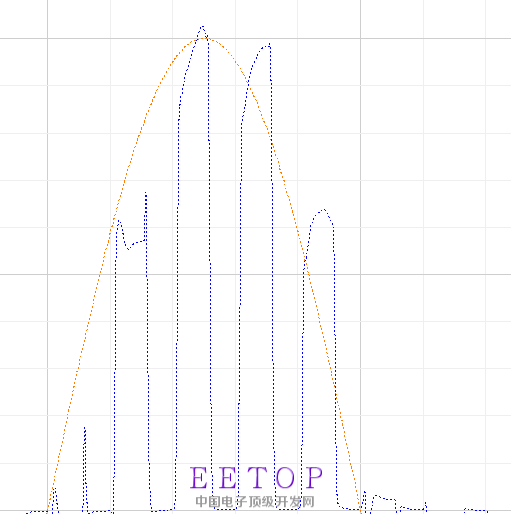

感觉第一个半周期波形还能看出点样子,然后接下来就感觉采样保持的波形跟输入波形比有延迟 而且还不降到0

感觉第一个半周期波形还能看出点样子,然后接下来就感觉采样保持的波形跟输入波形比有延迟 而且还不降到0

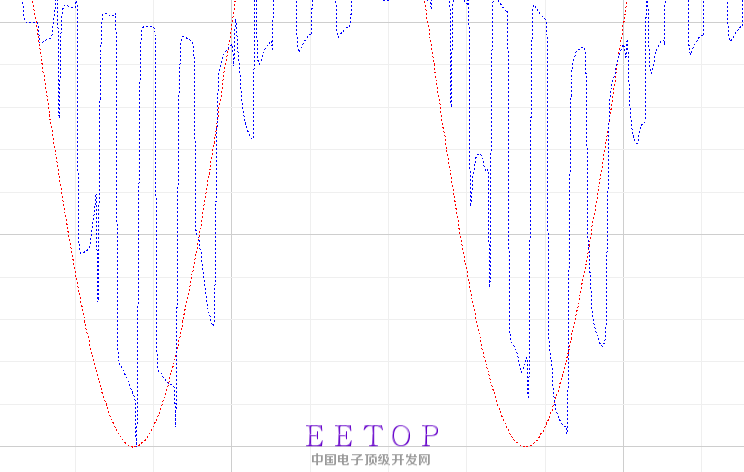

第二个图跟第三个图是分开的 不是合在一起的

4個可能 :

(1) OTA Slew Rate Not Enough, Current too small

(2) OTA Settling time Not Enough , means unity-gain frequency too low frequency

(3) Clock need non-overlap Clock

(4) ALL Switch Resistance need small enough , means MOS Width need Big enough

楼上正解 从图上看个人感觉(1)(2)可能性比较大

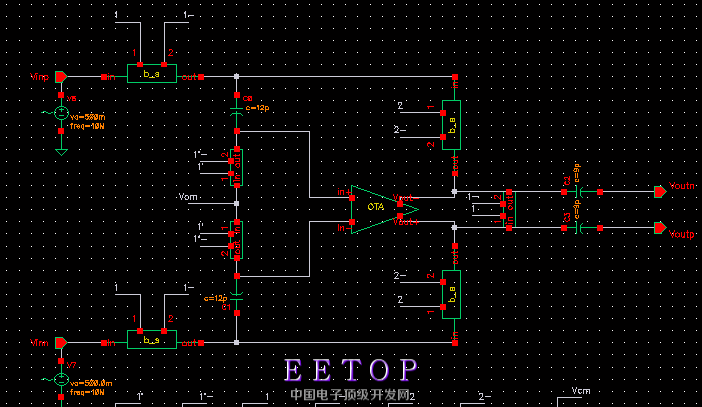

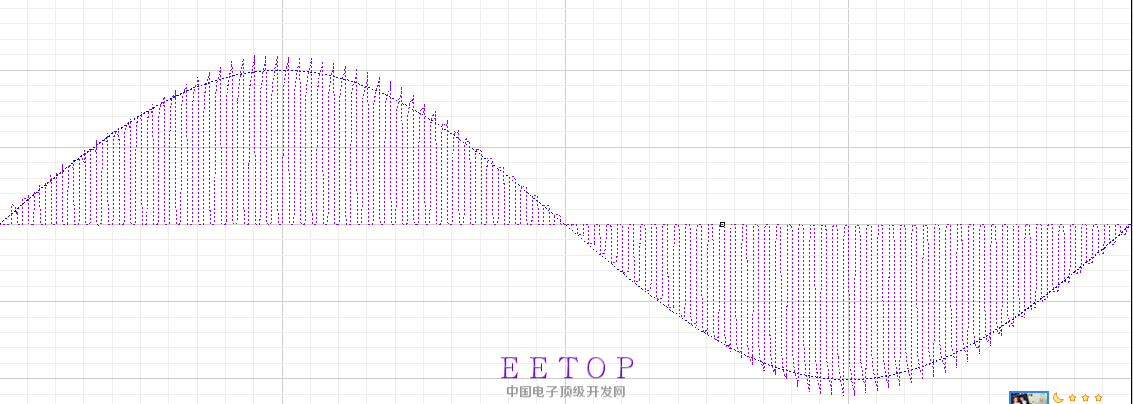

非常感谢,我刚刚把开关调了一下 电路图变成这样了

是不是还是需要调开关,还是OTA的问题呢?

是不是还是需要调开关,还是OTA的问题呢?  这个是输入1Mhz摆幅1V的图

这个是输入1Mhz摆幅1V的图

刚刚把开关调了一下 波形能降到0了 峰值也能到了 就是波形不正常

可以把采样频率降低,看下是不是前面两个的问题吧

非常感谢!我刚把采样周期加大 波形还是不对,我怀疑就是开关的问题,但是自举开关里面管子太多了(我用的是没改进过的经典的那个) 我不知道调哪个 。 本人还是本科 第一次cadence上做东西 运放还行 对自举开关这种东西完全是不懂。可以的话能不能指点一下。

共同学习

一定是 OTA Slew Rate 還是不夠,

運放的Current 與 MOS Width 要加大啊!

您可以觀察振幅比較小的地方已經在Hold mode Interval 是DC 了,

而在震幅比較大的地方,Hold Mode Interval 沒辦法維持DC.

频率降低、减小电容、加大电流

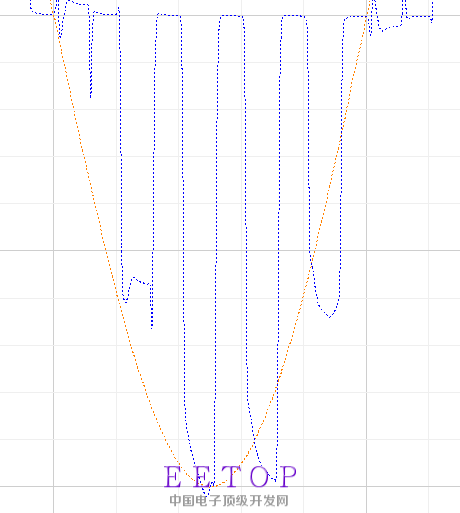

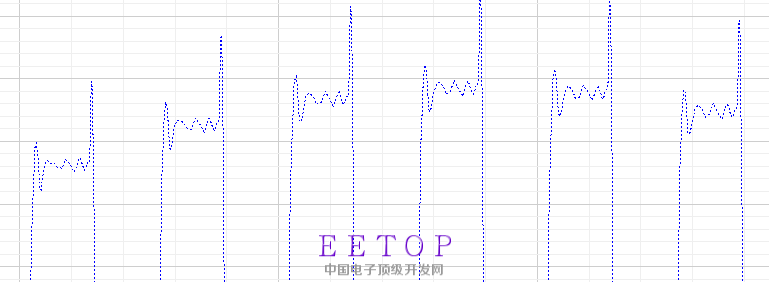

thanks,我把OTA改了一下,现在波形整体看挺正常的 , 就是拉大看保持波形变成这样了。

请问出现12L那种情况是怎么回事

settle time太长?

运放的建立时间还是 闭环电路的? 我该如何改进一下呢

Amplifier's close loop bandwidth too low frequency,

Close Loop Bandwidth = OP Unity-gain frequency * Beta

(Beta = feedback factor, in your case is ~ 0.5 )

so Only Extend your OP Unity-gain frequency to more high frequency,

the settling time will be improved.

你的settling time和sampling rate分别是多少?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:关于积分器的几个问题

下一篇:有哪位大侠用HFSS或CST做TSV设计的吗?