PLL不能锁定到指定频率

请指教这是什么原因造成的?

看看控制电压等于多少?

1, reference确定是5M而不是4.6875MHz?

2, loop lock了么?

如果lock了——那么可能你divider设计错了,要64确做了个60的;

3, 如果没有lock——那么可能你的vco最高工作频率只有300M

4, 如果没有lock——也可能是vctrl某个原因被限幅了,这要看你cp与vco之间的电路接口是怎么回事。

谢谢

首先我的参考频率的确是5MHz,divider也是64

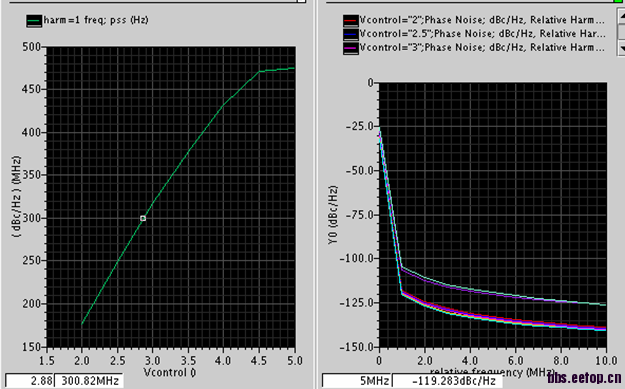

这是VCO的曲线

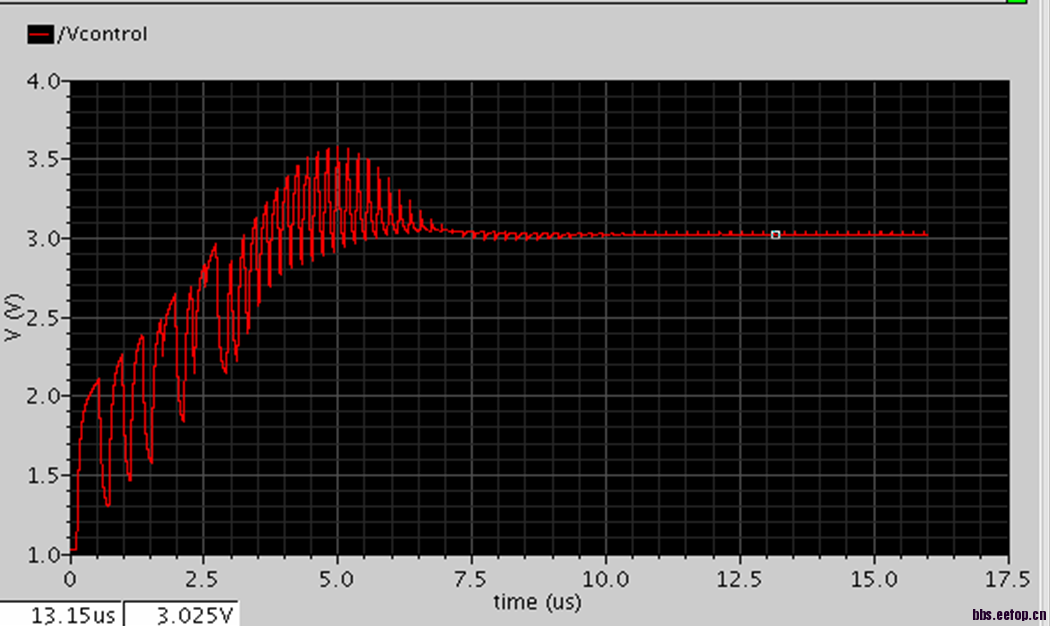

这是VCO的控制电压的曲线,

看了下,其实PLL最后的输出频率是314MHz。 这个频率合理吗?

把UP/DN信号拿出来看一下,如果没有phase err, 就OK了

很可能是你的VCO最高频率就只能这么高了!看看锁定指示是不是OK!

要320MHz,出来314MHz——当然不对了,肯定哪里出错了。

看起来VCO曲线正常从vctrl形状看锁定过程也正常,但有个疑问:10us之后感觉vctrl不干净,reference spur很大?把后面一段vctrl波形放大看清楚点,同时确定其没有问题。

还是怀疑divider和pfd这两个模块,建议仔细检查这两个模块的function

另外有人提到pfd固定相差,这个不会导致频率的偏差!频率有偏差了,相差会累积,不可能固定。仔细检查divider,有没有周期性丢掉cycle。

VCTL得出的曲线对应的频率不是准的,是有偏差的,和ADS的HB仿真是类似的,我看VC基本已经锁定了,你对transient做DFT才是准的真正的输出频率。

谢谢 我看了下 10us后VCO控制电压曲线的毛刺造成refrence spur很大, 如果想减小reference spur是不是应该减小PFD中的延时呢?

你怎么测量输出波形的频率呢?如果是计算器,那么截取的那段应该从稳定后的时间开始算起,否则就不对了。

可能是你的CP电流不匹配,或者Pfd 到达CP的脉冲信号时间不一样,可以单独拿出来仿真看看性能。

谢谢 关注。 频率使用计算器来测量的,

不好意思,上面的PLL的输出频率弄错了,不是314MHz,而是319.5MHz, 这样的话输出频率是否合理呢?

输入频率和分频器不可能是理想的,所以这样的话应该是合理的

我看了下pfd出来的信号到达时间是一致的, 但是就是cp的mismatch比较严重,有0.22uA,是不是这个mismatch太厉害了,导致VCO的控制电压在锁定后的毛刺比较严重

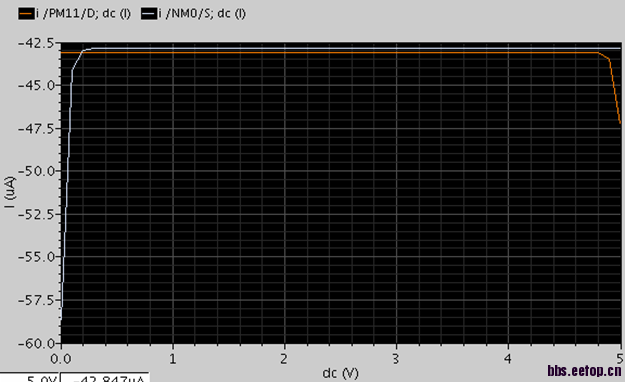

你充电电流多大呢?

CP的匹配精度要1%以内

按照楼上说的1%,你应该达标了,呵呵,不过我觉得还有提升的空间。

CP是什么结构啊?输出幅度都快railtorail了。

cp是差分结构

受教了,学些了.

顶起来

看看吧

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:运算放大器一般包含多少晶体管

下一篇:请教如何建立symbol的问题