请问INL为什么是这样的

录入:edatop.com 阅读:

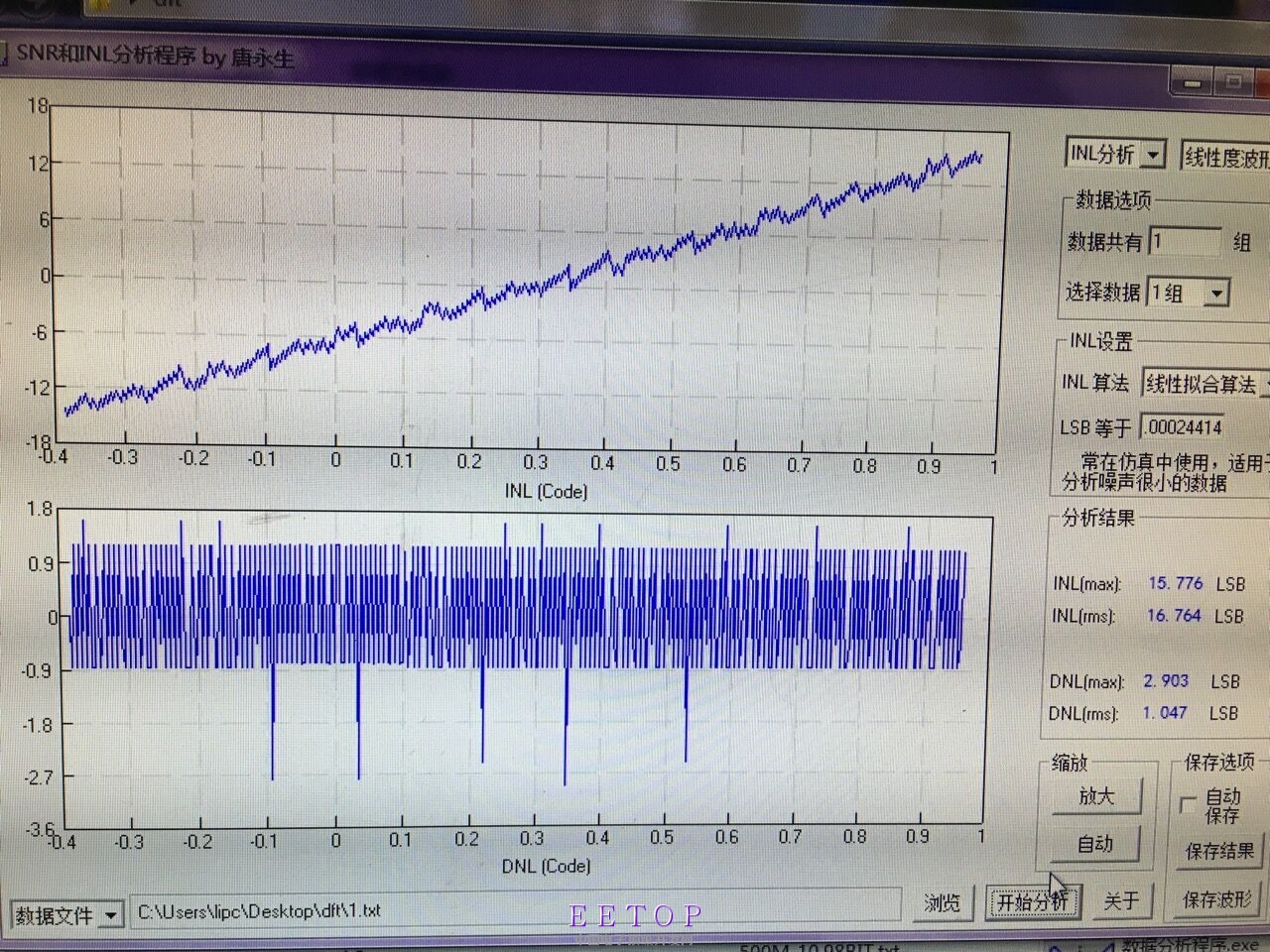

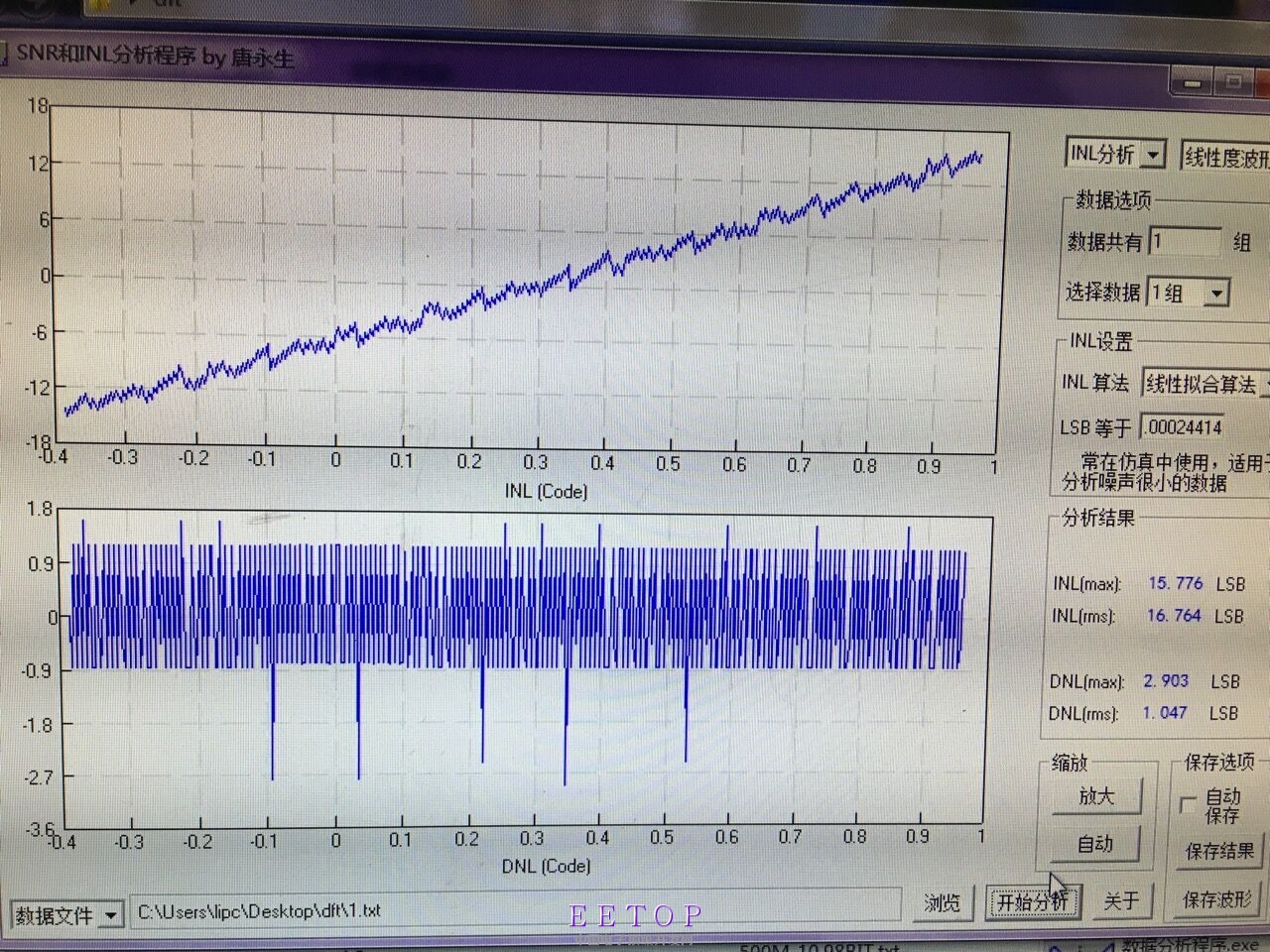

仿真12bits 流水线ADC的DNL和INL, ADC输出的数字码经过VerilogA写的DAC后,取512个点送到唐永生软件测DNL和INL,结果如下

1. 我用的是线性拟合算法,横坐标为什么不是0-4096?

2. 为什么INL一直增加,是因为增益失配吗?

3. 如果用码密度算法,出现提示“INL分析错误,请确认数据文件”,这是怎么回事?

请大神指点迷津,非常谢谢!

1. 我用的是线性拟合算法,横坐标为什么不是0-4096?

2. 为什么INL一直增加,是因为增益失配吗?

3. 如果用码密度算法,出现提示“INL分析错误,请确认数据文件”,这是怎么回事?

请大神指点迷津,非常谢谢!

很想知道,啥叫唐永生软件?

基本上仿真ADC的 DNL/INL 是不實際的,

通常需要點數 12-bit is 40960 點以上, (accuracy resolution < 0.1LSB)

DNL/INL的結果才會有意義的.

但您的電腦要算到40960點,

要算2個禮拜以上.

所以您還是放棄仿真DNL/INL , 一般都是實測DNL/INL .....

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。