管子参数调节的方法总结

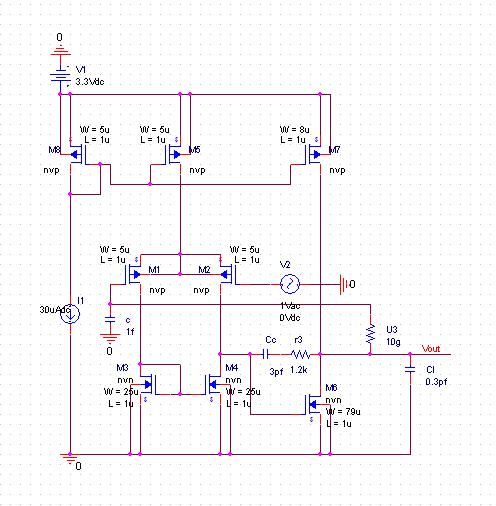

例如m6总处在线性区怎么调啊?

困惑的朋友们一起顶啊 盼高手总结!

以我浅见,输出管的比率失调,PMOS 的尺寸要做的大于NMOS尺寸,

你的电路中输出管PMOS尺寸太小,导致输出电流很小,这么小的电流,NMOS取79/1,

当然只能工作在线形区了,因为输入端电流镜负载导致NMOS删上的电压不能太低,不然它自己就不饱和了

方法:增大PMOS尺寸或减小NMOS尺寸

增大电流镜NMOS的尺寸,降低输出NMOS的删上电压高手! 受教了 能否总结一下

There is a fundmental error in your schematic. The DC level of input signal can not be "0".

从图上管子的尺寸来看,连最基本的常识都还没有了解,建议看看Gray的书中关于two stages op的内容。

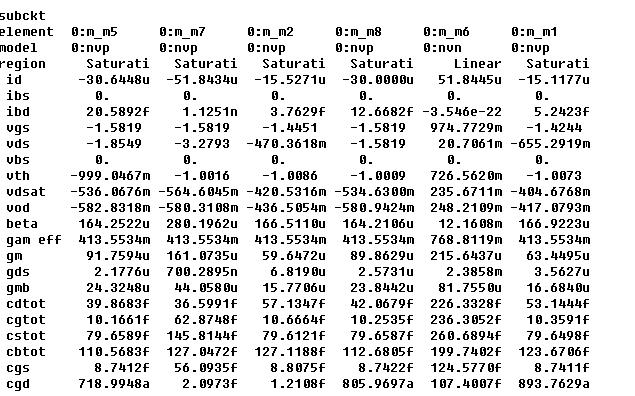

first stage以及two stage的bias current mirror 的管子W/L一般都是一样的,主要调节各自的M值来确定比例关系

OP的输入管子L值一般会取很小,W×L也不会太小,因为希望Match好一些,减小offset voltage

负载管子NMOS的尺寸有一点讲究,first stage的 I/(W/L)会等于second stage的 I/(W/L),

不希望带来系统失调。

另外管子的L值都取得这么小,可能会影响输出阻抗吧,增益会不会不够呢

补偿方面的东西就相对复杂一点,建议看书啦反馈使输出=0,你m6的Vds=0,还怎么饱和?

把输入DC电压调整一下 比如VCC/2,问题就解决了

当然你的系统失调和随机失调很大...M1栅电压通过反馈电阻U3可以获取,

M2为PMOS管,栅压直流偏值可以为0.

可将m6的w/l减小,增大m7的w/l,使m6处于饱和区.

第二级电流也要匹配,N管的尺寸按照第一级电流镜来匹配,跟上边P管电流相等

The DC bias voltage is not proper, anyway, if you set the input common voltage is 0, the transistor of M6 is alway woking in the linear region, suggest to simulate it under the condition of actual using in the system.

L=1u很大了 。

小编简单一想,你负反馈使得输出等于输入等于0v,即m6的vds是0v,你再怎么调它能饱和嘛

这个Sancen的书提到很多.

过驱动电压调好了,管子线性.可以将电流增大.

这个电路第二级的电流应该比第一级的大很多.使得非主极点在GBW外很多,当然由于有补偿电阻这个条件可以放宽一些.

另外负载电容应该如果是3pf ,然后那个米勒电容大概在1~2pf.申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:cadence的问题

下一篇:cadence hspice仿真