BW=1GHz的腔体带通滤波器时延怎么增强

录入:edatop.com 点击:

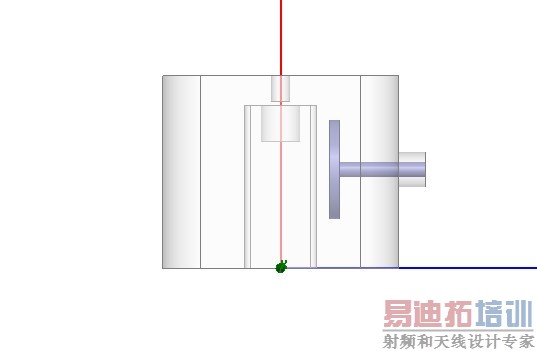

现在在做1700-2700的腔体带通滤波器,抽头形式只能用容性抽头,时延怎么也算不强,求助各位大神,怎么把时延做到理论值?

帮顶!!

只是单独的一路滤波器吗?楼主现在用的什么具体结构的抽头,是否可以展示图片,现在最好状态时延做到多少了?

一路带通加一路低通,带通时延现在有2ns左右,现在调试的结果看两路都需要加强

1.谐振器是方形的吗?方形侧边面积大,可以增强耦合

2.谐振器往端口靠近一些

3.抽头或者说你的连接器位置抬高一些

4.盘面继续加大,图片横着和连接器焊接的杆做粗些,或者做成阶梯状

记得公布你的最终结果噢。

1.谐振器是方形的,我调试的时候把谐振器周围都用铜皮围起来了,增大耦合面积

2.这个确实没考虑到

3.抽头的位置抬高过了

4.耦合器增大效果不是很明显。你说的阶梯状大概是什么样的

现在把低通的时延做弱,低通就很好,做强就很差

3.连接器的位置是否固定?可以改更的话,把连接器整提抬高

4.阶梯阻抗类似高低阻抗低通的样式

3.已经固定了,仿真的时候抬高作用已经不大了

4.了解

上一篇:HFSS滤波器有载Q值仿真,求助 啊 大神我爱你

下一篇:W波段微带滤波器仿真