- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

示波器“关键指标”—测量精确度和信号完整性

整个电子行业对速度及性能的不懈追求正不断改变高端示波器的标准。虽然当评估示波器时,带宽曾经是客户和销售商关注的“关键指标”,然而捕获和分析当今最快串行和光信号所需要的精确度(即:测量精确度和信号完整性)已经成为当前最重要的因素。

然而,什么是测量精确度?

带宽是一种用于比较一台仪器和另一台仪器差别的简单方式 ——具有最高带宽的那台一定是最好的,对吗?可以肯定的是,带宽是很重要的,对于高速应用而言,高带宽是必需的。然而,示波器的真正目的是要尽可能准确地显示感兴趣的信号,而且背后更为复杂,涉及仪器的基本设计、探头架构和连接配件、以及带宽之外的参数(包括上升时间、采样率和抖动本底噪声)。

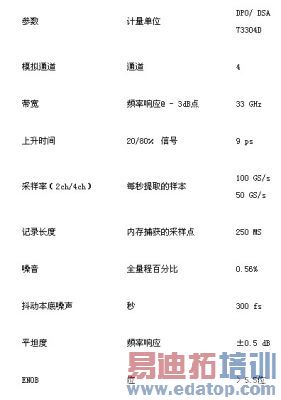

当选择示波器时,工程师应评估的关键参数概述如下表所示:

抖动本底噪声

市场驱动因素—— 需要更佳信号完整性

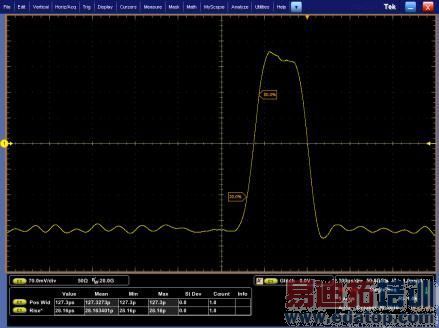

高速信号很容易产生信号完整性问题,因为它们涉及快沿和极窄的单位间隔或位次(bit times)。随着通信链路数据速率的增加,将增加两件事的发生:用户界面缩小,信号上升时间减少。例如,通过将 5 Gb / s 脉冲与 8 Gb / s 脉冲进行比较得出,位宽从 200 ps 降为 125 ps。这使得一项设计的裕量减小了 38%。此外,这也使得接收机的工作更加困难,因为它试图以更小的裕量,用非常快的数据速率将 1 与 0(零) 进行区分。同时,上升时间也从约 30ps 减少为刚好超过28 ps。8 GB / s 信号展示如下:

使问题复杂化的事实是,当被传输信号进入接收机时,可能产生多个信号完整性问题。这些信号完整性问题可能包括当此信号流经电路板或从硅芯片进入封装引脚再进入电路板时产生的信号衰减。通道内的信号衰减是一个非常严重的问题,必须加以解决。PCB 材料(如:FR – 4)内的信号损失量随线路长度的增加及数据速率的提高而增加。因信号幅度的缩小,噪音和反射正成为一个更大的影响因素。客户需要在接收机中采用去嵌入策略,以打开闭合的眼图。

随着第三代串行数据标准的出现,8-10 Gb / s正逐渐成为行业标准。在光通信市场中,因以太网(Ethernet)发展到 4 × 25G(100GbE),设计人员需要能够使用高达 32 Gb / s 的比特率对信号进行测试。同时,高速 FPGA 和宽带射频也推动了极限值的扩大。泰克公司的 DPO/DSA73304D 为这些高端应用程序提供业界最精准的测量性能。

技术平台与突破

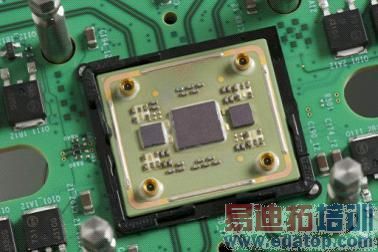

泰克公司为了提供业界领先的 DPO/DSA73304D 示波器性能,采用了 IBM 8HP 锗化硅技术。这是一种 130 纳米锗化硅双极互补金属氧化物半导体(BiCMOS)工艺,利用 200 GHz 的 FT 转换速度提供了 2 倍于上代产品的性能。

锗化硅(SiGe)技术利用可靠性高且成熟的制造工艺,提供能与特殊材料(如:磷化铟(InP)和砷化镓(GaAs))性能媲美的性能级别。与其它方案不同的是,锗硅BiCMOS工艺提供了在一块芯片上同时制备高速双极性晶体管和标准CMOS的途径,从而使一系列同时具备高集成度和极致性能的电路成为可能。正是这二者的结合,使泰克公司能够在长达十多年的时间内持续且可靠地提供功能丰富的高速数据采集系统。

图 1 所示的组件是采用了锗化硅 BiCMOS工艺的 70000D 示波器的新式前端,该前端为 33GHz、100 GS / s。该芯片包含 2 个通道(2 块小芯片)的前置放大器及一个 100 GS / s 的跟踪/保持集成电路(IC)(large die)。泰克公司通过将前置放大器和采样/保持功能集成于单一封装中,提高通道间的匹配能力,减少由其他示波器中使用的独立采样/保持电路和 ADC 器件引起的交叉失真。一般情况下,减少所需的组件和接口数量可减少噪音和计时的不确定性,从而提高了 ENOB 性能。

我们为此种前端设计提供的另一项创新是大偏移范围和终端性能。通过前置放大器芯片上的分离路径输入结构和多芯片模块上的 AC -接地端接电阻器,从而实现了此种性能。该性能可以更加轻松地对大型直流偏置或直流偏置终端信号做出准确的测量。

由于实现了向8HP的转换,DPO/DSA73304D示波器可以提供卓越的信号采集性能和分析能力。它帮助设计人员利用全部四通道前所未有的捕获功能够捕捉实时信号,并且利用业界最高的波形捕获能力捕获更多信号细节。利用一套工具集(为提供更快的设计和一致性测试而设计)实现设置、高速串行数据设计的捕获及分析的自动化。主要性能包括:

· 双通道高达 33 GHz 和 100 GS / s,所有四通道 > 20 GHz 和 50 GS / s

· 小于9 ps的上升时间(通常为 20/80)

· 低于 0.56% 的垂直噪声,≥5.5 的有效位数

· 30 多个可定制特殊应用软件分析包

示波器性能因素

由于示波器是设计方面(尤其是信号完整性方面)至关重要的工具,设计人员应熟悉示波器指标以及它们影响测量的方式。让我们观察一下最重要的三大因素 - 上升时间、采样率和带宽 – 从而对它们进行更深入的了解。

此示波器的上升时间越快,测量到的上升时间会越准确。但是,当示波器的带宽或上升时间和信号的上升时间彼此更接近时,会怎样呢? 有人曾用经验法则(如:0.35/上升时间)来计算所需的示波器带宽,但这种经验法则只适用于某些示波器的前端设计,并且通常不适用于为高速串行数据速率和伴随的快速上升时间而优化过的当今前端设计。

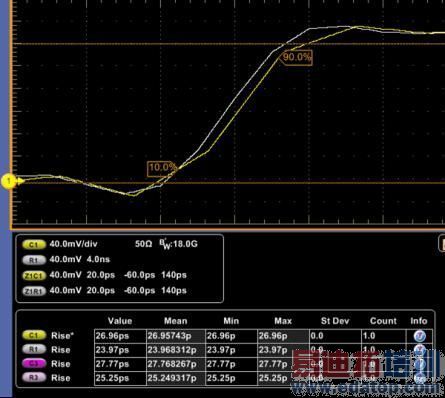

应当注意的是,具有相同带宽性能的两台示波器可以具有完全不同的上升时间、振幅和相位响应。所以,仅了解示波器的带宽无法可靠地揭示出其测量性能。此外,通过计算确定的上升时间可能也不准确。了解示波器上升和下降时间响应的最可靠方法是使用一个理想的阶跃信号对其进行测量,该理想的阶跃信号比被测示波器信号快很多。

在使用 DPO/DSA73304D 的情况下,使用这种方法确定 9 ps 的上升时间。但是,信号速度可以被测量的意思是什么呢?根据正确的经验法则,信号上升时间与示波器上升时间的比值为 2x 或 >18 ps。事实证明,对于当今最快的 FPGA 设计中使用的28 Gb / s 的串行解串器(SerDes)而言,这是指定的上升时间。

接下来,让我们看看另一个关键性能因素——示波器的实时采样率。因为更快的采样率带来更多的波形细节,所以这一因素非常重要。另一方面,对最快的信号而言,采样率不足可能会导致欠采样。此 DPO/DSA73304D 提供一流领先的采样率性能。利用交错技术提供采样率性能,此种交错技术使用 8 路采样/保持方法,将杂散高频的影响降至最低。参见以下数据,可得出被成功和失败执行的交错技术的差异:

成功的交错,频率杂散较少 失败的交错,频率杂散且有噪声

奈奎斯特定理(Nyquist theorem)指出,采样系统应对输入信号的最高频率采样 2 次以上。虽然这是最低起始点,但是在任何情况下,采样率越高,结果越准确。通过使用 2.5 倍较高采样率,此输入频率或更多输入频率可提供被关注信号上的更多采样点,且避免混叠。对于极高速信号表征而言,这是特别重要的。

下图显示了较高的采样率值。**跟踪线(C1)在 50 GS / s 上,而白色跟踪线(R1)在 100 GS / s 上。过采样原因包括:

· 为确保信号中已知和未知的高频部分被捕获,且没有混叠

· 为实现卓越的定时分辨率(特别是快速瞬态信号或边缘上的定时分辨率)

· 作为一种减少测量中噪音的手段。采样过密会减少量化噪声,产生的此类量化噪声是示波器中 A 向 D 转换的一部分

在此带宽前端,示波器必须有足够的带宽来捕捉高频部分,以便准确地显示信号的转换。 然而,当销售商为带宽需求进行善意提示,推荐 5 次谐波时,事情在不断发生变化。边沿速率(上升/下降时间)的变化并没有与数据速率的变化同步。这意味着,所需的最大带宽受到上升时间的影响更大。例如,目前第三代规格的上升时间在 30ps 的范围内。随着速率的不断提高,这似乎并没有很大变化,这表明,相对于数据速率的信号谐波含量正在下降。

详细了解精确度和强大捕获能力

新型 DPO/DSA73304D 平台兼备业界领先的实时示波器信号完整性和计时精度,使用户能够更准确和更有把握地完成他们的设计。它可以帮助他们:

· 利用业界最精准的捕获系统,发现感兴趣的重要信号,此类捕获系统的特征是采用了在示波器和探头中使用的可靠锗化硅技术。

· 使用市场上最佳综合触发系统,捕获高速信号评估所需的精确的信号事件。

· 利用高采样率搜寻记录,以确定关键事件/错误,用于系统验证。

· 利用 30 + GHz 示波器中最高信号与嗓音的比值,快速分析关键测量结

果。它能够提供高灵敏度、低噪声的测量结果,这样的结果为高速光纤的

准确定性及能源和串行数据测量的执行提供依据。

尖端软件与 DPO/DSA70000 系列平台上用户界面工具相互结合,为复杂测量方案(包括调试/分析)提供了最短的快速响应时间。

DPO/DSA73304D 通过结合高带宽、高采样率和快速上升时间,可为当今最高的信号完整性测量要求而特别进行量身定做。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:V波段近距探测毫米波功率放大器设计

下一篇:X波段LNA设计