- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

覆铜时安全距离设置问题 求助

报错信息说的是顶层的焊盘与铜皮间距规则不满足...具体什么样你最好截图发上来看看...

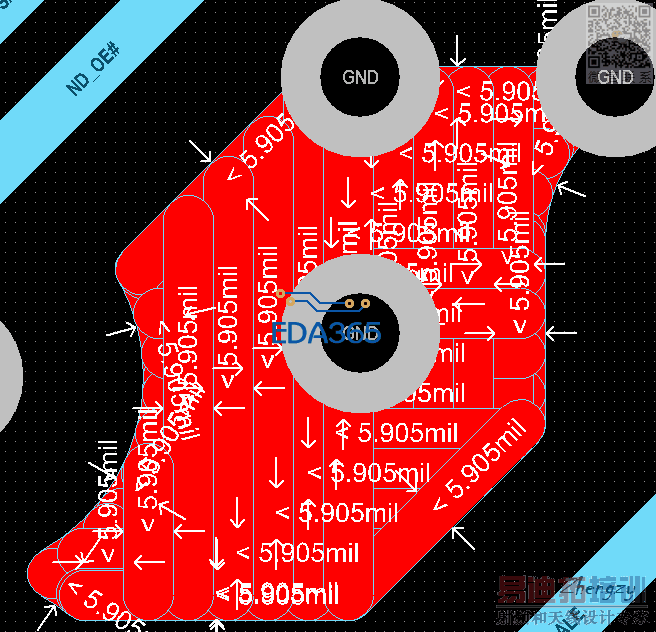

栅格距离我设置为0.1mm,图中红色为GND覆铜区域,绿色为VCC覆铜区域两个区域的距离为两个半栅格,和我设置的安全距离0.254mm符合。上方的两个红色1GND,2GND为元件引脚。中间的1VCC为接线线焊盘。

我也见过这种情况,就是就是铺铜时,一块整体的铜一部分在room里,一部分不在,room里的间距规则小,就会出现图片右边的情况,解决方法就是,铺两块铜,不要让一块铜跨越room

你看一下规则的优先级是不是设错了

我这个电路板由于产品设计要求必须正极大面积覆铜,所以对VCC覆铜时我是选中整个电路板的,这个和room有关系吗?

酱紫,你没截图之前回复的,突然想到自己遇到铺铜怪异的情况,你看看是不是规则的优先级的问题

你的这个报错并不是因为你的GND的铜皮和VCC的铜皮间距报错....你图片截图地方不对...你的图片的左下角部分那里貌似有什么东西也报错了...

左下角那部分是因为元器件两个引脚焊盘需要通过走线相连,其中一个焊盘由于是特殊焊盘,所以我采用了方形焊盘和椭圆形焊盘叠加组合的方式,这一部分我没有选择网络表形式,这个错误可以忽略吧?

这样貌似找不到问题的所在啊...方便的话你就把PCB文件发上来吧...一起看看找找原因...

你图中显示的那个是孔的大小不对吧?,我跨BGA也没有报错啊

你可以设置一个room的区间规则,这样就不会报错了啊

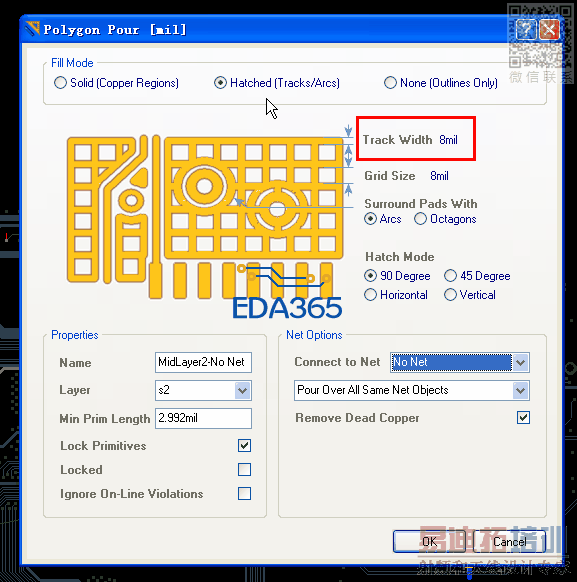

请查看下你的敷铜线宽是否满足线宽规则,不满足线宽规则的话也会报错的

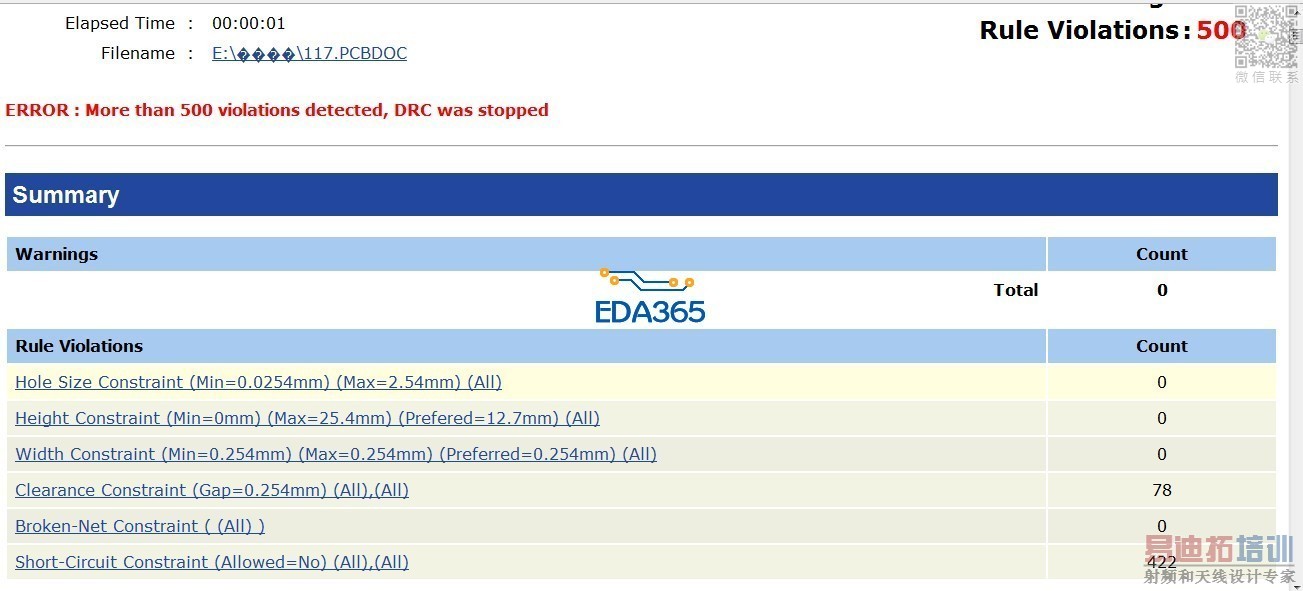

设计规则检查之后出现如图所示的错误分配:

从你这张图能够看出来你把你的线宽定死了..都是10mil..而AD里面polygon默认属性的线宽是8mil

有可能是这里导致你的铜皮都会报错....

看你的另外两张图片上面都是说的是polygon与pad直接的间距问题....能不能把你rules的clearance部分的所有规则设置和你报错的地方截图几张传上来....PCB上报错的地方多截图几张最好....

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:Altium 菜单设置问题

下一篇:元件拖动时连线也跟着拖动